- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379094 > CY7C43644 (Cypress Semiconductor Corp.) 1K x36 x2 Bidirectional Synchronous FIFO w/ Bus Matching(1K x36 x2 雙向同步先進先出帶總線匹配) PDF資料下載

參數(shù)資料

| 型號: | CY7C43644 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 1K x36 x2 Bidirectional Synchronous FIFO w/ Bus Matching(1K x36 x2 雙向同步先進先出帶總線匹配) |

| 中文描述: | 每1000 x36 x2雙向同步FIFO瓦特/總線匹配(每1000 x36 x2雙向同步先進先出帶總線匹配) |

| 文件頁數(shù): | 23/37頁 |

| 文件大?。?/td> | 581K |

| 代理商: | CY7C43644 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

CY7C43624

CY7C43634/CY7C43644

CY7C43664/CY7C43684

23

PRELIMINARY

Notes:

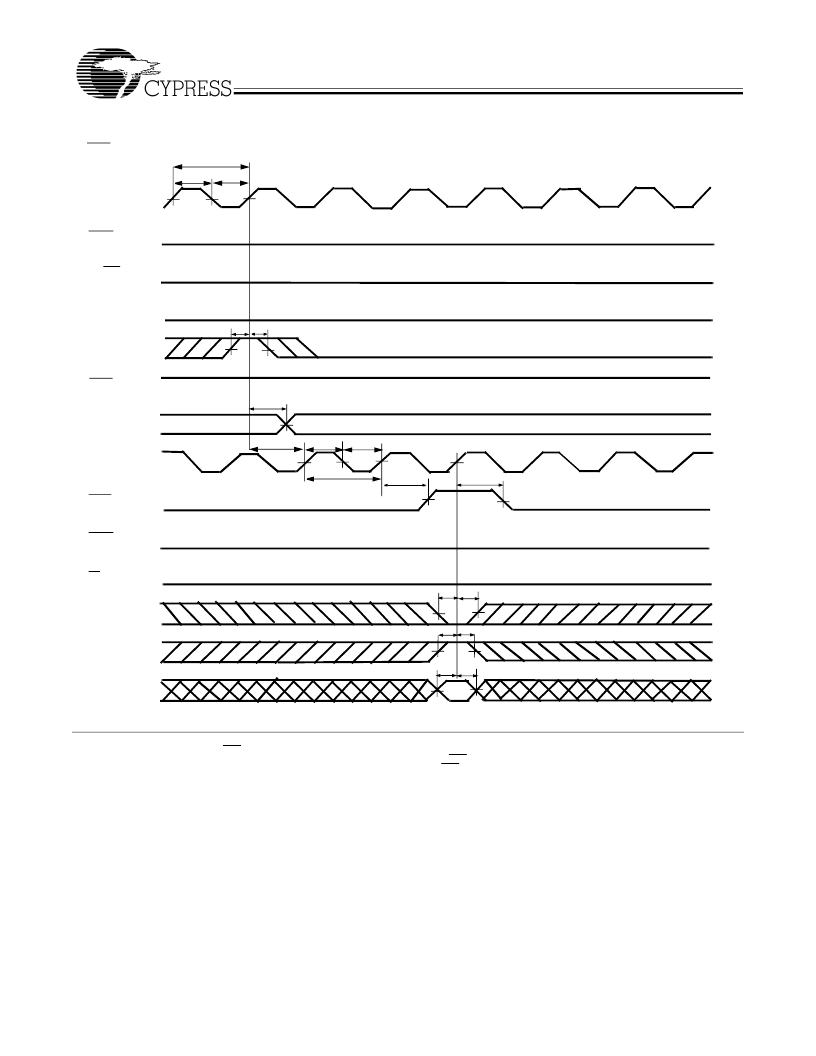

35. If Port B size is word or byte, FFB is set LOW by the last word or byte write of the long-word, respectively.

36. t

is the minimum time between a rising CLKA edge and a rising CLKB edge for FFB to transition HIGH in the next CLKB cycle. If the time between the

rising CLKA edge and rising CLKB edge is less than t

SKEW1

, then the transition of FFB HIGH may occur one CLKB cycle later than shown.

Switching Waveforms

(continued)

t

CLKH

t

CLKL

t

ENS

t

ENH

t

A

LOW

LOW

HIGH

FIFO2 Full

LOW

LOW

t

ENS

t

ENH

t

WFF

t

WFF

t

CLKH

t

CLKL

t

CLK

t

CLK

t

SKEW1[36]

t

DH

t

DS

t

ENH

t

ENS

Previous Word in FIFO12 Output Register

Next Word From FIFO2

To FIFO2

LOW

CLKA

CSA

W/RA

MBA

ENA

EFA/ORA

A

0

–

35

CLKB

FFB/IRB

CSB

W/RB

MBB

ENB

B

0

–

35

FFB Flag Timing and First Available Write when FIFO2 is Full (CY Standard Mode)

[35]

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C43664 | 4K x36 x2 Bidirectional Synchronous FIFO w/ Bus Matching(4K x36 x2 雙向同步先進先出帶總線匹配) |

| CY7C43684 | 16K x36 x2 Bidirectional Synchronous FIFO w/ Bus Matching(16K x36 x2 雙向同步先進先出帶總線匹配) |

| CY7C43636 | 512 x36/x18x2 Tri Bus FIFO(512 x36/x18x2 三路總線 先進先出) |

| CY7C43626 | 256 x36/x18x2 Tri Bus FIFO(256 x36/x18x2 三路總線先進先出) |

| CY7C43646 | 1K x36/x18x2 Tri Bus FIFO(1K x36/x18x2 三路總線 先進先出) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C43644AV-10AC | 制造商:Cypress Semiconductor 功能描述:FIFO Mem Sync Dual Depth/Width Bi-Dir 1K x 36 x 2 128-Pin TQFP |

| CY7C43663-15AC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C43664-7AC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C43682-15AC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C43683-10AI | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。