- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379006 > CY28341ZC (CYPRESS SEMICONDUCTOR CORP) Universal Single-Chip Clock Solution for VIA P4M266/KM266 DDR Systems PDF資料下載

參數(shù)資料

| 型號: | CY28341ZC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | XO, clock |

| 英文描述: | Universal Single-Chip Clock Solution for VIA P4M266/KM266 DDR Systems |

| 中文描述: | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 6 X 14 MM, TSSOP2-56 |

| 文件頁數(shù): | 11/21頁 |

| 文件大?。?/td> | 189K |

| 代理商: | CY28341ZC |

CY28341

Document #: 38-07367 Rev. *A

Page 11 of 21

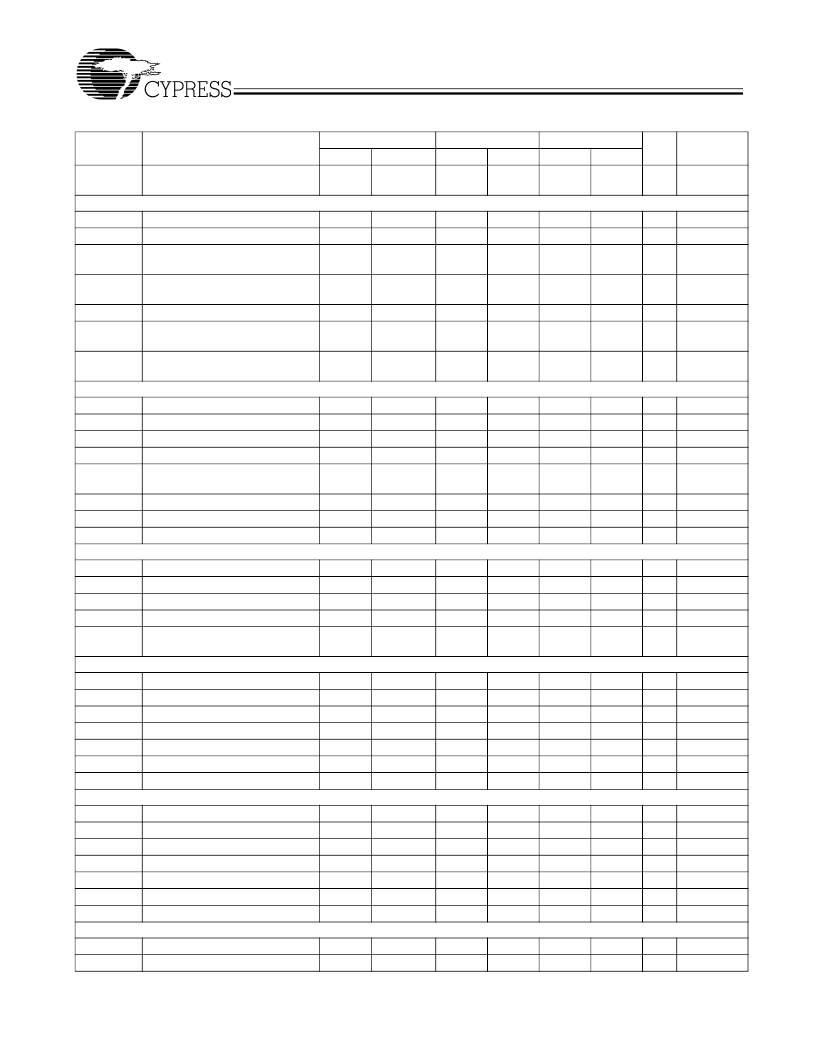

Vcross

Crossing Point Voltage at 0.7V

Swing

P4 Mode CPU at 1.0V

TDC

CPUT/C Duty Cycle

TPeriod

CPUT/C Period

Differential

Tr/Tf

TSKEW

CPUCS_T/C to CPUT/C Clock

Skew

TCCJ

CPUT/C Cycle to Cycle Jitter

Vcross

Crossing Point Voltage at 1V

Swing

SE-

DeltaSlew

Waveform Symmetry

K7 Mode

TDC

CPUOD_T/C Duty Cycle

TPeriod

CPUOD_T/C Period

TLOW

CPUOD_T/C LOW Time

Tf

CPUOD_T/C Fall Time

TSKEW

CPUCS_T/C to CPUT/C Clock

Skew

TCCJ

CPUOD_T/C Cycle to Cycle Jitter

VD

Differential Voltage AC

VX

Differential Crossover Voltage

CHIPSET CLOCK

TDC

CPUCS_T/C Duty Cycle

TPeriod

CPUCS_T/C Period

Tr / Tf

CPUCS_T/C Rise and Fall Times

VD

Differential Voltage AC

VX

Differential Crossover Voltage

280

430

280

430

280

430

mV

22

45

9.85

175

55

10.2

467

45

7.35

175

55

7.65

467

45

4.85

175

55

5.1

467

%

nS

ps

11,14,21

11,14,21

13,15,25

CPUT/C Rise and Fall Times

0

200

0

150

0

200

0

11,15,21

–

150

510

+150

760

–

150

510

+150

760

–

200

510

+200

760

ps

mV

11,15,21

26

Absolute Single-ended Rise/Fall

325

325

325

ps

24,31

45

9.98

2.8

0.4

0

55

10.5

45

7.5

1.67

0.4

0

55

8.0

45

5

2.8

0.4

0

55

5.5

%

ns

ns

ns

0

11,14

11,14

11,14

11,13

11,15,21

1.6

200

1.6

150

1.6

200

–

150

0.4

500

+150

Vp+.6V

1100

–

150

0.4

500

+150

Vp+.6V

1100

–

200

0.4

500

+200

Vp+.6V

1100

ps

V

mV

11,14

20

19

45

10.0

0.4

0.4

0.5*V

DDI

–

0.2

55

10.5

1.6

Vp+.6V

0.5*V

DDI

+

0.2

45

15

0.4

0.4

55

15.5

1.6

Vp+.6V

0.5*V

DDI

+ 0.2

45

10.0

0.4

0.4

0.5*V

DDI

–

0.2

55

10.5

1.6

Vp+.6V

0.5*V

DDI

+ 0.2

%

ns

ns

V

V

7,11,14

7,11,14

7,11,13

27

21

0.5*V

DDI

–

0.2

AGP

TDC

TPeriod

THIGH

TLOW

Tr / Tf

TSKEW

TCCJ

PCI

TDC

TPeriod

THIGH

TLOW

Tr / Tf

TSKEW

TCCJ

48MHz

TDC

TPeriod

AGP(0:2) Duty Cycle

AGP(0:2) Period

AGP(0:2) HIGH Time

AGP(0:2) LOW Time

AGP(0:2) Rise and Fall Times

Any AGP to Any AGP clock Skew

AGP(0:2) Cycle to Cycle Jitter

45

15

5.25

5.05

0.4

55

16

45

15

5.25

5.05

0.4

55

16

45

15

5.25

5.05

0.4

55

16

%

ns

ns

ns

ns

ps

ps

7,11,14

7,11,14

11,16

11,17

11,13

11,15

11,14,15

1.6

250

500

1.6

250

500

1.6

250

500

PCI(_F,1:6) Duty Cycle

PCI(_F,1:6) Period

PCI(_F,1:6) HIGH Time

PCI(_F,1:6) LOW Time

PCI(_F,1:6) Rise and Fall Times

Any PCI to Any PCI Clock Skew

PCI(_F,1:6) Cycle to Cycle Jitter

45

30.0

12.0

12.0

0.5

55

45

30.0

12.0

12.0

0.5

55

45

30.0

12.0

12.0

0.5

55

%

ns

ns

ns

ns

ps

ps

7,11,14

7,11,14

11,16

11,17

11,13

11,15

11,14,15

2.5

500

500

2.5

500

500

2.5

500

500

48MHz Duty Cycle

48MHz Period

45

55

45

55

45

55

%

ns

7,11,14

7,11,14

20.8299

20.8333

20.8299 20.8333 20.8299 20.8333

AC Parameters

(continued)

Parameter

Description

100 MHz

Min.

133MHz

Min.

200 MHz

Min.

Unit

Notes

[4]

Max.

Max

Max

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY28341ZCT | Universal Single-Chip Clock Solution for VIA P4M266/KM266 DDR Systems |

| CY28341OCT | Universal Single-Chip Clock Solution for VIA P4M266/KM266 DDR Systems |

| CY28341OC | Universal Single-Chip Clock Solution for VIA P4M266/KM266 DDR Systems |

| CY28346 | Clock Synthesizer with Differential CPU Outputs |

| CY28346OC | CONN BNC PLUG CRIMP RG-TFE-59,62 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY28341ZC-2 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Universal Clock Chip for VIA⑩P4M/KT/KM400 DDR Systems |

| CY28341ZC-2T | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Universal Clock Chip for VIA⑩P4M/KT/KM400 DDR Systems |

| CY28341ZC-3 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Universal Clock Chip for VIA⑩P4M/KT/KM400A DDR Systems |

| CY28341ZC-3T | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Universal Clock Chip for VIA⑩P4M/KT/KM400A DDR Systems |

| CY28341ZCT | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Universal Single-Chip Clock Solution for VIA P4M266/KM266 DDR Systems |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。