- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378985 > CXD3068Q (Sony Corporation) CD Digital Signal Processor with Built-in Digital Servo(CD數(shù)字信號處理器(內(nèi)置數(shù)字伺服系統(tǒng))) PDF資料下載

參數(shù)資料

| 型號: | CXD3068Q |

| 廠商: | Sony Corporation |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | CD Digital Signal Processor with Built-in Digital Servo(CD數(shù)字信號處理器(內(nèi)置數(shù)字伺服系統(tǒng))) |

| 中文描述: | CD數(shù)字信號處理器具有內(nèi)置的數(shù)字式伺服(光盤數(shù)字信號處理器(內(nèi)置數(shù)字伺服系統(tǒng))) |

| 文件頁數(shù): | 90/135頁 |

| 文件大小: | 1259K |

| 代理商: | CXD3068Q |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁當(dāng)前第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁

– 90 –

CXD3068Q

§ 5-4. E:F Balance Adjustment Function (See Fig. 5-3.)

When the disc is rotated with the laser on, and with the FCS (focus) servo on via FCS Search (focus search),

the traverse waveform appears in the TE signal due to disc eccentricity.

In this condition, the low-frequency component can be extracted from the TE signal using the built-in TRK hold

filter by setting D5 (TBLM) of $38 to 1.

The extracted low-frequency component is loaded into the TRVSC register as a digital value, and the TRVSC

register value is established when TBLM returns to "0".

Next, setting D2 (TLC2) of $38 to 1 compensates the values obtained from the TE and SE input pins with the

TRVSC register value (subtraction), allowing the E:F balance offset to be adjusted. (See Fig. 5-3.)

§ 5-5. FCS Bias (Focus Bias) Adjustment Function

The FBIAS register value can be added to the FCS servo filter input by setting D14 (FBON) of $3A to 1. (See

Fig. 5-3.)

When D11 = 0 and D10 = 1 is set by $34F, the FBIAS register value can be written using the 9-bit value of D9

to D1 (D9: MSB).

In addition, the RF jitter can be monitored by setting the $8 command SOCT to 1. (See "DSP Block Timing

Chart".)

The FBIAS register can be used as a counter by setting D13 (FBSS) of $3A to 1. The FBIAS register functions

as an up counter when D12 (FBUP) of $3A = 1, and as a down counter when D12 (FBUP) of $3A = 0.

The number of up and down steps can be changed by setting D11 and D10 (FBV1 and FBV0) of $3A.

When using the FBIAS register as a counter, the counter stops when the value set beforehand in FBL9 to

FBL1 of $34 matches the FCSBIAS value. Also, if the upper 8 bits of the command register are $3A at this

time, SENS goes to high and the counter stop can be monitored.

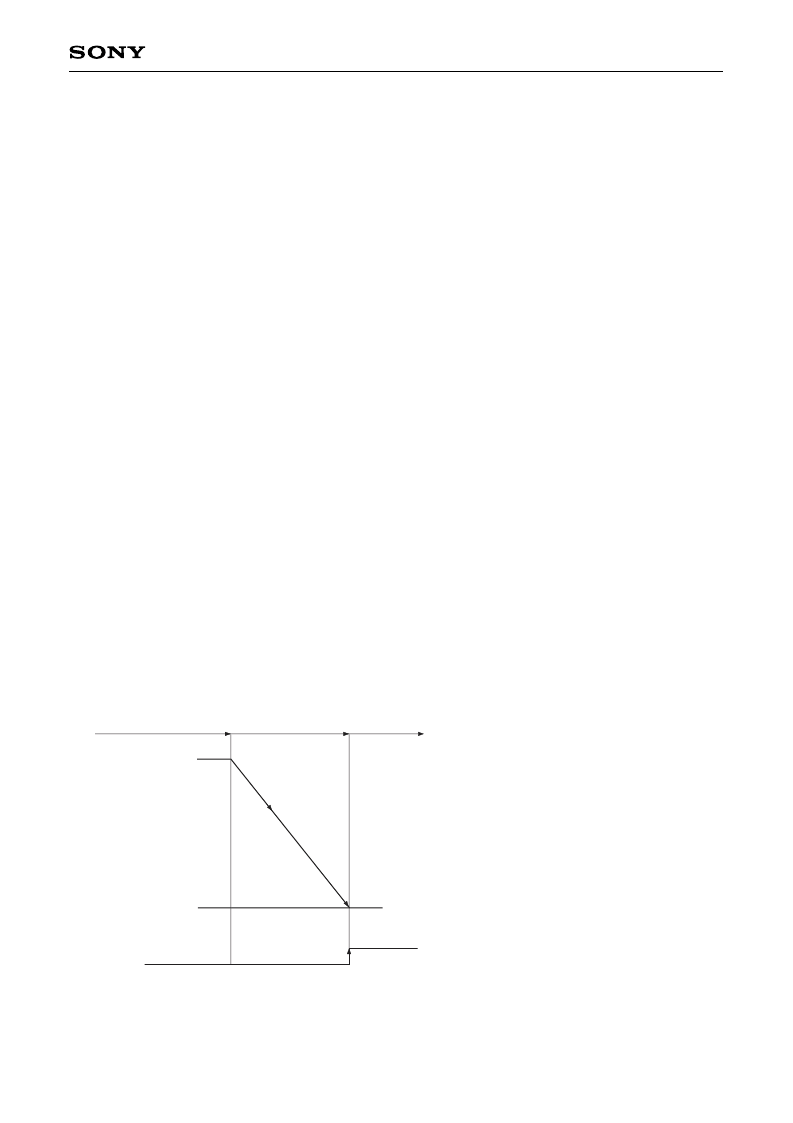

Here, assume the FBIAS setting value FB9 to

FB1 and the FBIAS LIMIT value FBL9 to FBL1

are set in status A. For example, if command

registers FBUP = 0, FBV1 = 0, FBV0 = 0 and

FBSS = 1 are set from this status, down count

starts from status A and approaches the set

LIMIT value. When the LIMIT value is reached

and the FBIAS value matches FBL9 to FBL1,

the counter stops and the SENS pin goes to

high. Note that the up/down counter counts at

each sampling cycle of the focus servo filter.

The number of steps by which the count value

changes can be selected from 1, 2, 4 or 8 steps

by FBV1 and FBV0. When converted to FE

input, 1 step corresponds to 1/512

×

V

DD

×

0.4.

A

B

C

FBIAS setting value

(FB9 to FB1)

LIMIT value

(FBL9 to FBL1)

SENS pin

A: Register mode

B: Counter mode

C: Counter mode (when stopped)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CXD3152AR | Signal Processor LSI for Single-chip CCD B/W Camera |

| CXD3400 | 6-channel CCD Vertical Clock Driver |

| CXD3400N | Silver Mica Capacitor; Capacitance:30000pF; Capacitance Tolerance: 2%; Series:CD42; Voltage Rating:500VDC; Capacitor Dielectric Material:Mica; Termination:Radial Leaded; Lead Pitch:27mm; Leaded Process Compatible:No RoHS Compliant: No |

| CXD3410 | Timing Generator and Signal Processor for Frame Readout CCD Image Sensor |

| CXD3410GA | Timing Generator and Signal Processor for Frame Readout CCD Image Sensor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CXD3141 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ccd-cmosIC資料 |

| CXD3142R | 制造商:SONY 制造商全稱:Sony Corporation 功能描述:Signal Processor LSI for Single-Chip CCD Color Camera |

| CXD3152AR | 制造商:SONY 制造商全稱:Sony Corporation 功能描述:Signal Processor LSI for Single-chip CCD B/W Camera |

| CXD3152R | 制造商:SONY 制造商全稱:Sony Corporation 功能描述:Signal Processor LSI for Single-chip CCD B/W Camera |

| CXD3172AR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Signal Processor LSI for Single CCD Color Camera |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。