- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369673 > CSP1027 CSP1027 Voice Band Codec for Cellular Handset and Modem Applications PDF資料下載

參數(shù)資料

| 型號: | CSP1027 |

| 元件分類: | Codec |

| 英文描述: | CSP1027 Voice Band Codec for Cellular Handset and Modem Applications |

| 中文描述: | CSP1027語音頻帶編解碼器的蜂窩手機和調(diào)制解調(diào)器應(yīng)用 |

| 文件頁數(shù): | 54/64頁 |

| 文件大小: | 937K |

| 代理商: | CSP1027 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁當(dāng)前第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

CSP1027 Voice Band Codec for

Cellular Handset and Modem Applications

Data Sheet

December 1999

Lucent Technologies Inc.

54

10 Analog Characteristics and Requirements

(continued)

10.4 Miscellaneous

* The codec is intended to drive a floating 2 k

load, such as a telephone handset speaker, or 1 k

loads ac-coupled to ground on both ana-

log outputs. Since the codec outputs AOUTP and AOUTN have common-mode dc voltage, ac coupling must be used if there is a dc path to

V

DD

or V

SS

(ground) through the load.

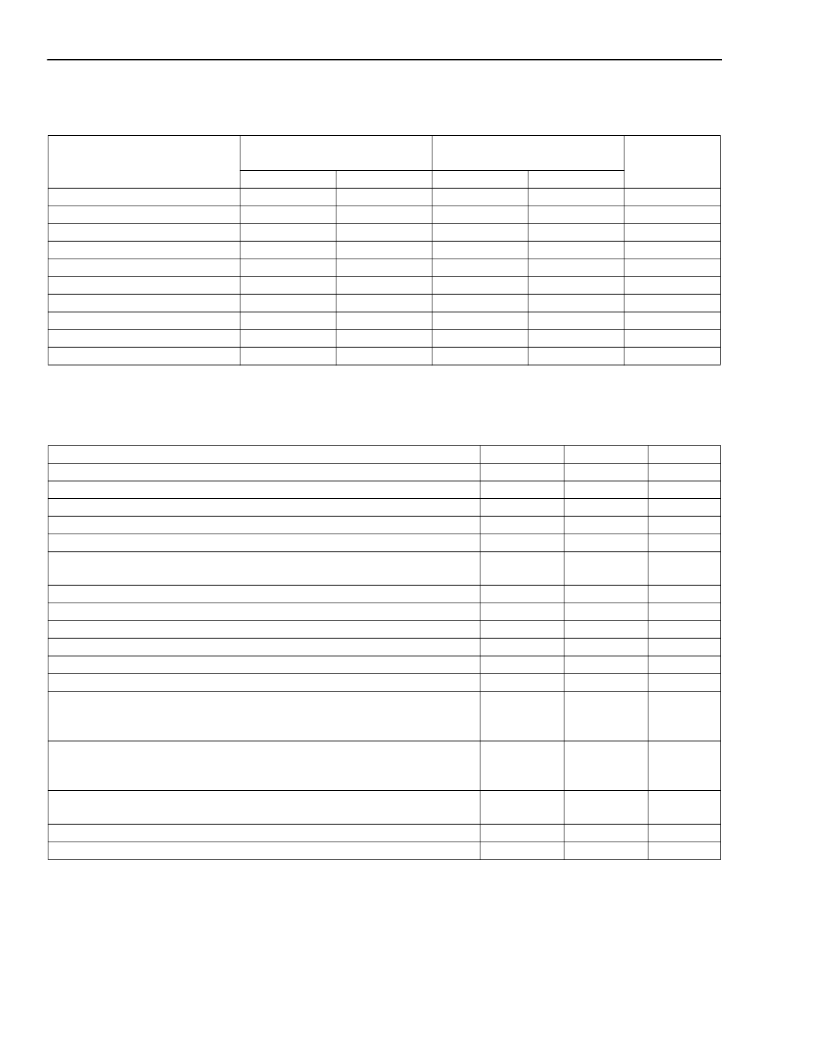

Table 22. D/A Frequency Response Relative to 1 kHz Output Level (f

OS

= 1 MHz and f

S

= 8 kHz)

Frequency

High-Pass Filter Enabled

(HPFE = 0)

Min

50 Hz

—

60 Hz

—

100 Hz

–34

200 Hz

–12

300 Hz

–0.25

3000 Hz

–0.25

3400 Hz

–0.9

4000 Hz

—

4600 Hz

—

8000 Hz

—

High-Pass Filter Disabled

(HPFE = 1)

Min

–0.25

–0.25

–0.25

–0.25

–0.25

–0.25

–0.9

—

—

—

Unit

Max

–40

–40

–18

0

0.25

0.25

0.25

–6

–35

–45

Max

0.25

0.25

0.25

0.25

0.25

0.25

0.25

–6

–35

–45

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

Table 23. Other Analog Characteristics and Requirements*

Parameter

D/A Differential Output Resistance (0 kHz to 4 kHz)

D/A Single-ended Output Resistance (0 kHz to 4 kHz)

Analog-to-Digital Power Supply Rejection Ratio at 3 kHz

Digital-to-Analog Power Supply Rejection Ratio at 3 kHz

Analog Input Coupling Capacitor Input Leakage Current

Idle Channel Noise at Analog-to-Digital Output with Input Gain Setting of

500 mVp or 160 mVp

Idle Channel Noise at Digital-to-Analog Output

A/D to D/A and D/A to A/D Crosstalk

Digital-to-Analog Image Frequency Attenuation Above 4600 Hz

Digital-to-Analog Output Amplifier Differential Swing for 2 k

Load

Codec Filter Group Delay for Frequencies Less than 800 Hz

Codec Filter Group Delay for Frequencies Greater than 800 Hz

Recovery Time of Digital-to-Analog Output Due to a Change from Inac-

tive Mode to Active Mode, Muted to Not Muted, or Change in Output

Gain (See

cioc0

register, ACTIVE, MUTE, OGSEL.)

Recovery Time of Analog-to-Digital PCM Output and V

REG

Due to a

Change from Inactive Mode to Active Mode (See

cioc0

register,

ACTIVE.)

Recovery Time of Analog Circuits Due to a Change in Input Select or

Input Range (See

cioc0

register, INSEL and IRSEL.)

Allowable CLK Input Jitter

Allowable CLK Frequency Error

Min

—

—

30

40

—

—

Max

12

6

—

—

30

–65

Unit

dB

dB

nA

dBm0

—

—

35

—

—

—

—

300

–65

—

1.5

2.8

0.8

100

μVrms

dB

dB

Vrms

ms

ms

ms

—

600

ms

—

100

ms

–5

–1

5

1

ns

%

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CT1469-2 | CT1469-2 MIL-STD-1397 Type E 10MHz Transceiver |

| CT1496-2 | CT1496-2 MIL-STD-1397 Type E 10MHz Low Level Serial Manchester 32 Bit Encoder |

| CT1508-2 | CT1508-2 MIL-STD-1397 Type E 10MHz Serial Manchester 4-Bit SIS / SOS Decoder |

| CT1611 | DMA Controller with Buffer Memory,MIL-STD-1750A Compatible |

| CT1611-FP | DMA Controller with Buffer Memory,MIL-STD-1750A Compatible |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CSP1027J | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Linear CODEC |

| CSP1027-J11-DB | 制造商:Alcatel-Lucent 功能描述: |

| CSP1027S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Linear CODEC |

| CSP1027-S11-DB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CSP1034AH | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。