- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369673 > CSP1027 CSP1027 Voice Band Codec for Cellular Handset and Modem Applications PDF資料下載

參數(shù)資料

| 型號(hào): | CSP1027 |

| 元件分類: | Codec |

| 英文描述: | CSP1027 Voice Band Codec for Cellular Handset and Modem Applications |

| 中文描述: | CSP1027語音頻帶編解碼器的蜂窩手機(jī)和調(diào)制解調(diào)器應(yīng)用 |

| 文件頁數(shù): | 21/64頁 |

| 文件大?。?/td> | 937K |

| 代理商: | CSP1027 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

Lucent Technologies Inc.

21

Data Sheet

December 1999

CSP1027 Voice Band Codec for

Cellular Handset and Modem Applications

4 Architectural Information

(continued)

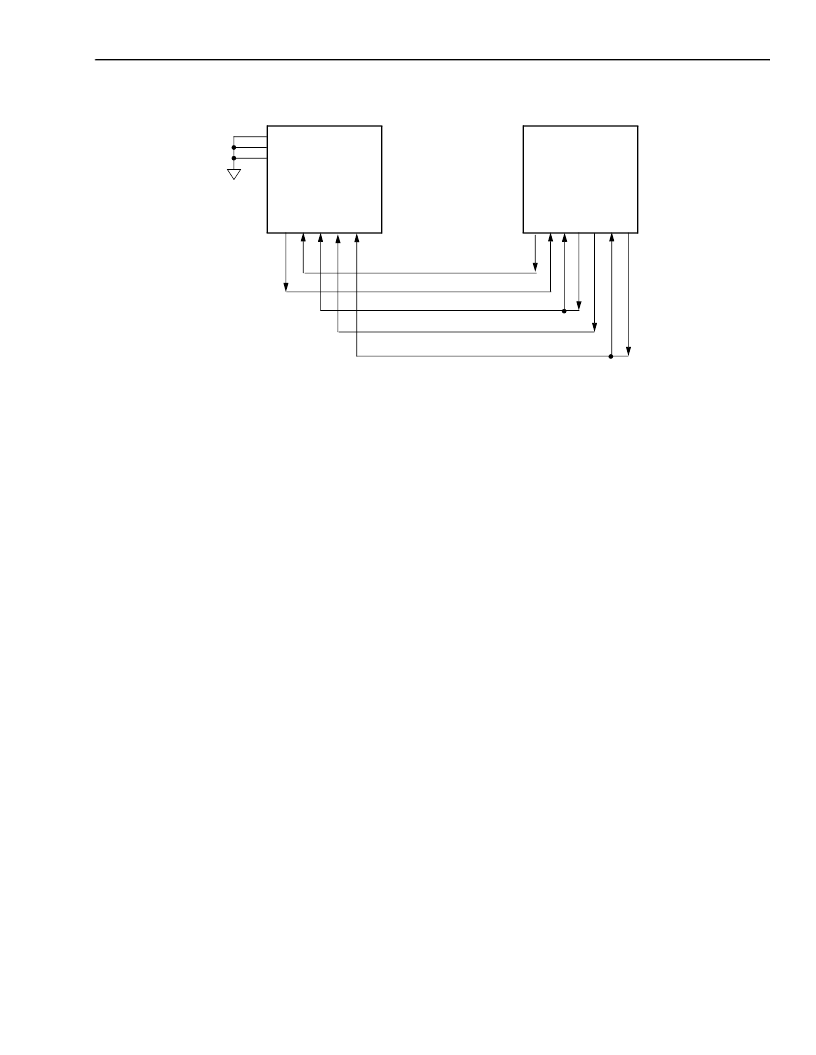

Figure 22. Passive Communication and Connections

4.6.4 Passive I/O Configuration (SMODE[1:0] = 00)

The passive SIO configuration allows the user maxi-

mum flexibility in interfacing the CSP1027 to a variety

of system hardware configurations. It requires that the

user supply a serial input/output clock (IOCK) and per-

form data transfers at the sampling rate, f

S

. Serial data

transfers can be made to occur at the sampling rate by

applying a clock that is synchronous with the codec

clock, ICLK, to the SYNC pin or by polling the codec

STATUS flag, which indicates that the

cdx(A/D)

regis-

ter is full and the

cdx(D/A)

register is empty. The STA-

TUS flag appears on DO when the SADD pin selects a

control word.

Passive SIO is selected by setting both SMODE1 and

SMODE0 low. The input/output clock (IOCK) is an input

and the common input/output load, SYNC, (equivalent

to a DSP16A's ILD and OLD tied together) is also an

input. Serial data input (DI) is an input and serial data

output, DO, is an output. The serial address (SADD) is

an input, which determines if the transfer is to the con-

trol registers,

cioc

[0:3], or the data register,

cdx(D/A)

.

A high-to-low transition of SYNC pin signal, latched by

the next rising edge of IOCK, initiates the start of an

input and output transaction. If the CSP1027's output

buffer,

cdx(A/D)

, is full, it will be loaded into the output

shift register (

osr

) and shifted out on the DO pin. The

CSP1027 shifts in the data from the DI pin into its input

shift register (

isr

). A serial transmit address on the

SADD line is received simultaneously with data on the

DI line. If SADD is high for the first 15 bits, correspond-

ing to a zero serial transmit address, this causes the

isr

to be latched into

cdx(D/A)

after 16 bits have been

shifted in. If SADD is low for any of the first 15 bits, cor-

responding to a nonzero transmit address, this causes

the

isr

to be latched into

cioc

[0:3] and also changes

the output data stream on DO to display the internal

codec STATUS flag. If SADD is low for any clock cycle,

while not involved in a serial transaction, the codec

STATUS flag is displayed on the DO pin until the next

data transfer.

An example of the passive SIO configuration is shown

in Figure 22. The DSP supplies both the serial clock

(IOCK) and the sampling synchronization signal to

SYNC, or polls the internal codec STATUS flag to

determine when a data transmission is needed. This

configuration allows the user maximum flexibility in

interfacing the CSP1027 to a variety of other system

hardware configurations.

A/D DATA

CLOCK

CONTROL/DATA ADDRESS

INPUT/OUTPUT LOAD

D

I

I

O

D

O

D

I

S

S

D

DSP

CSP1027

SMODE0

SMODE1

SMODE2

D/A DATA

S

5-7590 (F)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CT1469-2 | CT1469-2 MIL-STD-1397 Type E 10MHz Transceiver |

| CT1496-2 | CT1496-2 MIL-STD-1397 Type E 10MHz Low Level Serial Manchester 32 Bit Encoder |

| CT1508-2 | CT1508-2 MIL-STD-1397 Type E 10MHz Serial Manchester 4-Bit SIS / SOS Decoder |

| CT1611 | DMA Controller with Buffer Memory,MIL-STD-1750A Compatible |

| CT1611-FP | DMA Controller with Buffer Memory,MIL-STD-1750A Compatible |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CSP1027J | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Linear CODEC |

| CSP1027-J11-DB | 制造商:Alcatel-Lucent 功能描述: |

| CSP1027S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Linear CODEC |

| CSP1027-S11-DB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CSP1034AH | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。