- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4069 > CS80C286-12 (Intersil)IC CPU 16BIT 5V 12.5MHZ 68-PLCC PDF資料下載

參數(shù)資料

| 型號: | CS80C286-12 |

| 廠商: | Intersil |

| 文件頁數(shù): | 18/60頁 |

| 文件大小: | 0K |

| 描述: | IC CPU 16BIT 5V 12.5MHZ 68-PLCC |

| 標準包裝: | 126 |

| 處理器類型: | 80C286 16-位 |

| 速度: | 12.5MHz |

| 電壓: | 5V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 68-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 68-PLCC(24.23x24.23) |

| 包裝: | 管件 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

25

function of the IRET instruction. If NT = 0, the IRET instruc-

tion performs the regular current task by popping values off

the stack; when NT = 1, IRET performs a task switch opera-

tion back to the previous task.

When a CALL, JMP, or INT instruction initiates a task switch,

the old (except for case of JMP) and new TSS will be

marked busy and the back link field of the new TSS set to

the old TSS selector. The NT bit of the new task is set by

CALL or INT initiated task switches. An interrupt that does

not cause a task switch will clear NT. NT may also be set or

cleared by POPF or IRET instructions.

The task state segment is marked busy by changing the

descriptor type field from Type 1 to Type 3. Use of a selec-

tor that references a busy task state segment causes

Exception 13.

Processor Extension Context Switching

The context of a processor extension is not changed by the

task switch operation. A processor extension context need

only be changed when a different task attempts to use the

processor extension (which still contains the context of a pre-

vious task). The 80C286 detects the first use of a processor

extension after a task switch by causing the processor exten-

sion not present exception (7). The interrupt handler may then

decide whether a context change is necessary.

Whenever the 80C286 switches tasks, it sets the Task

Switched (TS) bit of the MSW. TS indicates that a proces-

sor extension context may belong to a different task than

the current one. The processor extension not present

exception (7) will occur when attempting to execute an

ESC or WAIT instruction if TS = 1 and a processor exten-

sion is present (MP = 1 in MSW).

Pointer Testing Instructions

The 80C286 provides several instructions to speed pointer

testing and consistency checks for maintaining system integ-

rity (see Table 18). These instructions use the memory man-

agement hardware to verify that a selector value refers to an

appropriate segment without risking an exception. A condition

flag (ZF) indicates whether use of the selector or segment will

cause an exception.

Double Fault and Shutdown

If two separate exceptions are detected during a single

instruction execution, the 80C286 performs the double fault

exception (8). If an exception occurs during processing of

the double fault exception, the 80C286 will enter shutdown.

During shutdown no further instructions or exceptions are

processed. Either NMI (CPU remains in protected mode) or

RESET (CPU exits protected mode) can force the 80C286

out of shutdown. Shutdown is externally signalled via a

HALT bus operation with A1 LOW.

Protected Mode lnitialization

The 80C286 initially executes in real address mode after

RESET. To allow initialization code to be placed at the top of

physical memory. A23-20 will be HIGH when the 80C286

performs memory references relative to the CS register until

CS is changed. A23-20 will be zero for references to the DS,

ES, or SS segments. Changing CS in real address mode will

force A23-20 LOW whenever CS is used again. The initial

CS:lP value of F000:FFF0 provides 64K bytes of code space

for initialization code without changing CS.

Protected mode operation requires several registers to be

initialized. The GDT and IDT base registers must refer to a

valid GDT and IDT. After executing the LMSW instruction to

set PE, the 80C286 must immediately execute an intraseg-

ment JMP instruction to clear the instruction queue of

instructions decoded in real address mode.

To force the 80C286 CPU registers to match the initial pro-

tected mode state assumed by software, execute a JMP

instruction with a selector referring to the initial TSS used in

the system. This will load the task register, local descriptor

table register, segment registers and initial general register

state. The TR should point at a valid TSS since any task

switch operation involves saving the current task state.

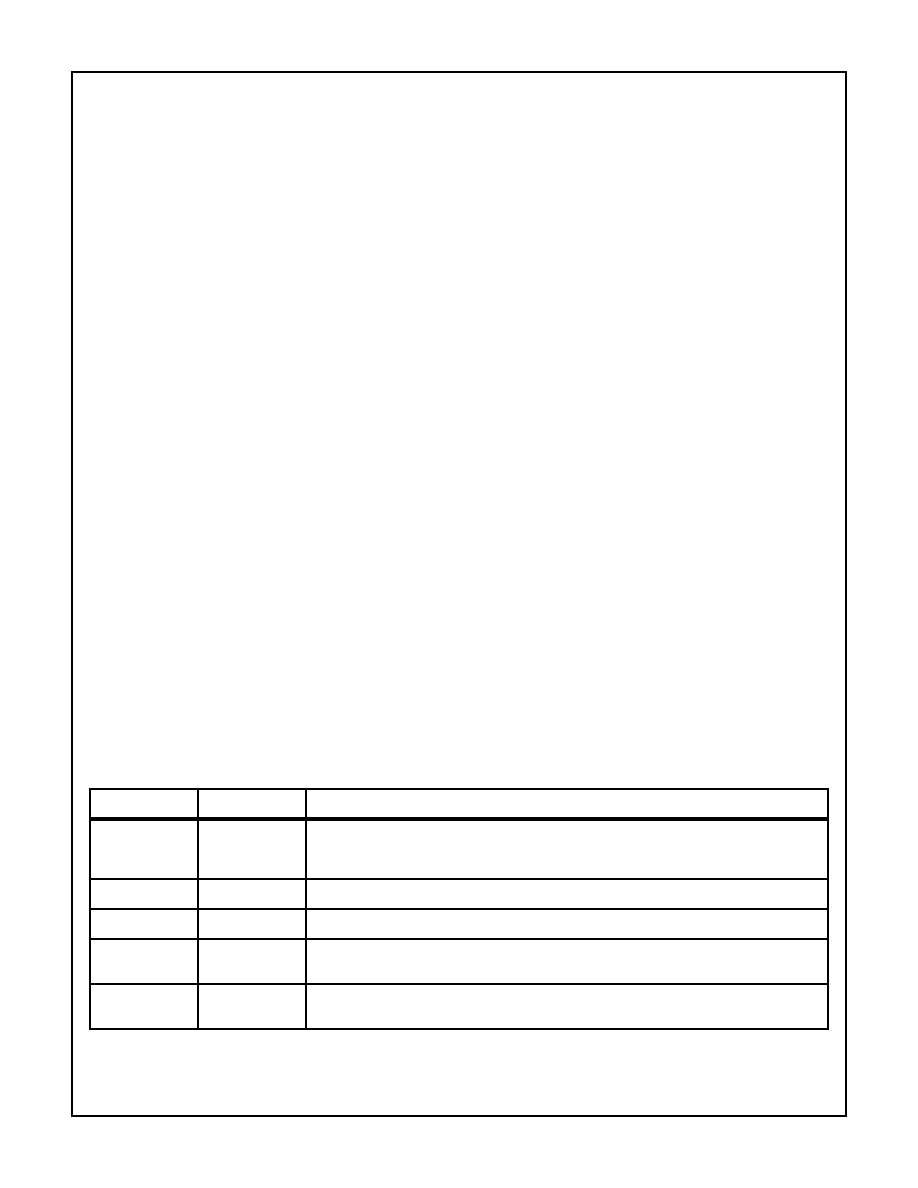

TABLE 18. 80C286 POINTER TEST INSTRUCTIONS

INSTRUCTION

OPERANDS

FUNCTION

ARPL

Selector,

Register

Adjust Requested Privilege Level: adjusts the RPL of the selector to the numeric maximum of

current selector RPL value and the RPL value in the register. Set zero flag if selector RPL was

changed by ARPL.

VERR

Selector

VERify for Read: sets the zero flag if the segment referred to by the selector can be read.

VERW

Selector

VERify for Write: sets the zero flag if the segment referred to by the selector can be written.

LSL

Register,

Selector

Load Segment Limit: reads the segment limit into the register if privilege rules and descriptor type

allow. Set zero flag if successful.

LAR

Register,

Selector

Load Access Rights: reads the descriptor access rights byte into the register if privilege rules al-

low. Set zero flag if successful.

80C286

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IP80C88 | IC CPU 8/16BIT 5V 5MHZ 40-DIP |

| SPC5200CBV400B | IC MPU 32BIT 500MHZ 272PBGA |

| ABB85DHBR | CONN EDGECARD 170PS R/A .050 SLD |

| XF2M-2215-1A | CONN FPC 22POS 0.5MM PITCH SMD |

| MPC859TCVR100A | IC MPU POWERQUICC 100MHZ 357PBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CS80C286-1296 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS80C286-12X136 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS80C286-16 | 功能描述:微處理器 - MPU CPU 16BIT 5V CMOS 16 MHZ 68PLCC COM RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| CS80C286-1696 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS80C286-2 | 制造商:Harris Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。