- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295174 > BX805499030 (INTEL CORP) 64-BIT, 1600 MHz, MICROPROCESSOR, CPGA611 PDF資料下載

參數(shù)資料

| 型號: | BX805499030 |

| 廠商: | INTEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 64-BIT, 1600 MHz, MICROPROCESSOR, CPGA611 |

| 封裝: | PGA-611 |

| 文件頁數(shù): | 107/108頁 |

| 文件大小: | 2315K |

| 代理商: | BX805499030 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁當前第107頁第108頁

98

Dual-Core Intel Itanium Processor 9000 Series Datasheet

Signals Reference

A.1.27

DPS# (I/O)

The Deferred Phase Enable (DPS#) signal is driven to the bus on the second clock of

the Request Phase on the Ab[3]# pin. DPS# is asserted if a requesting agent supports

transaction completion using the Deferred Phase. A requesting agent that supports the

Deferred Phase will always assert DPS#. A requesting agent that does not support the

Deferred Phase will always deassert DPS#.

A.1.28

DRDY# (I/O)

The Data Ready (DRDY#) signal is asserted by the data driver on each data transfer,

indicating valid data on the data bus. In a multi-cycle data transfer, DRDY# can be

deasserted to insert idle clocks.

DRDY# is replicated three times to enable partitioning of data paths in the system

agents. This copy of the Data Ready signal (DRDY#) is an input as well as an output.

A.1.29

DRDY_C1# (O)

DRDY# is a copy of the Data Ready signal. This copy of the Data Phase data-ready

signal (DRDY_C1#) is an output only.

A.1.30

DRDY_C2# (O)

DRDY# is a copy of the Data Ready signal. This copy of the Data Phase data-ready

signal (DRDY_C2#) is an output only.

A.1.31

DSZ[1:0]# (I/O)

The Data Size (DSZ[1:0]#) signals are transferred on REQb[4:3]# signals in the

second clock of the Request Phase by the requesting agent. The DSZ[1:0]# signals

define the data transfer capability of the requesting agent. For the processor, DSZ# =

01, always.

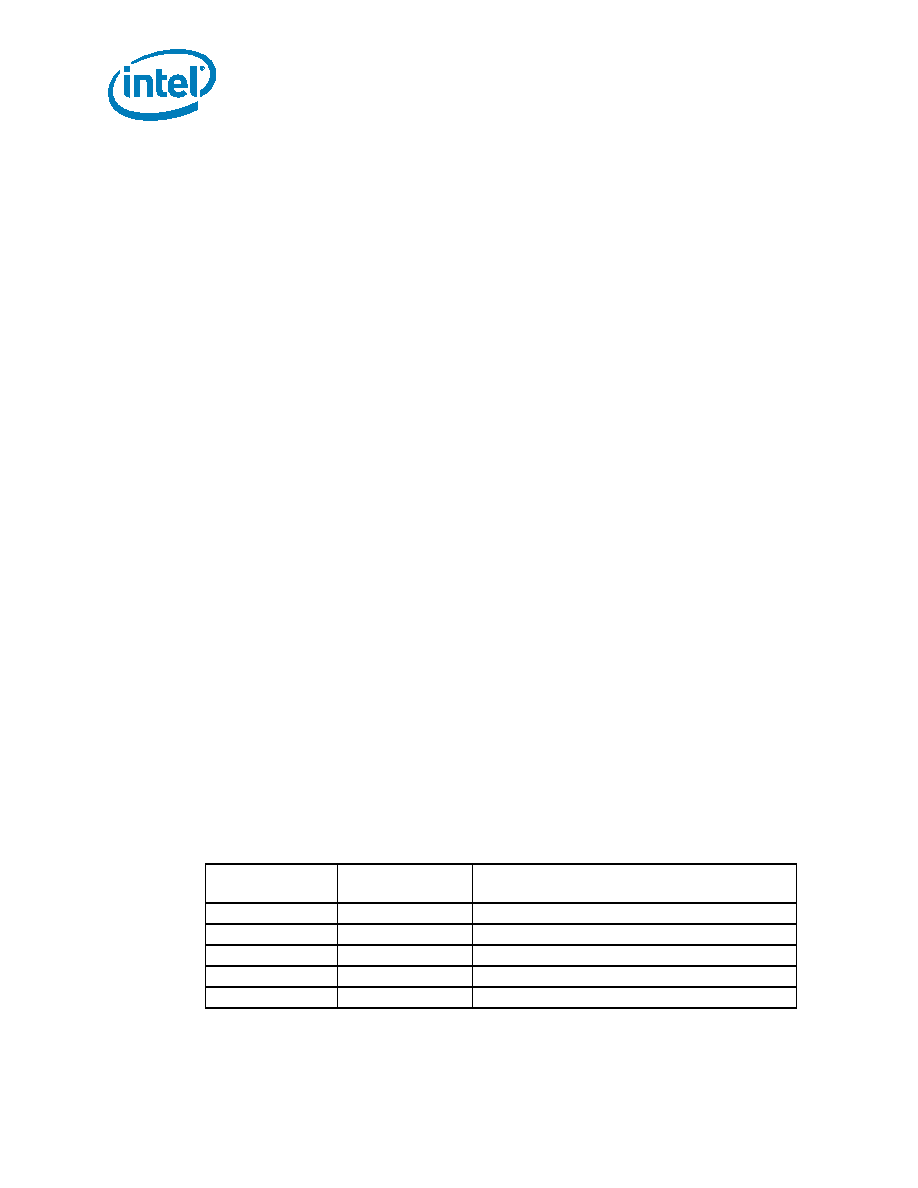

A.1.32

EXF[4:0]# (I/O)

The Extended Function (EXF[4:0]#) signals are transferred on the A[7:3]# pins by the

requesting agent during the second clock of the Request Phase. The signals specify any

special functional requirement associated with the transaction based on the requestor

mode or capability. The signals are defined in Table A-8.

Table A-8.

Extended Function Signals

Extended Function

Signal

Signal Name Alias

Function

EXF[4]#

Reserved

EXF[3]#

SPLCK#/FCL#

Split Lock / Flush Cache Line

EXF[2]#

OWN#/CCL#

Memory Update Not Needed / Cache Cleanse

EXF[1]#

DEN#

Defer Enable

EXF[0]#

DPS#

Deferred Phase Supported

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BX805499040 | 64-BIT, 1600 MHz, MICROPROCESSOR, CPGA611 |

| BXA10-12D15-S | 2-OUTPUT DC-DC REG PWR SUPPLY MODULE |

| BXA200-48S12 | 1-OUTPUT 200 W DC-DC REG PWR SUPPLY MODULE |

| BXA40-48S15 | 1-OUTPUT 40 W DC-DC REG PWR SUPPLY MODULE |

| BXB100-48S15FLTJ | 1-OUTPUT 100 W DC-DC REG PWR SUPPLY MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BX805499040 | 制造商:Intel 功能描述:DUAL-CORE ITANIUM 1.60 GHZ - Boxed Product (Development Kits) |

| BX805499050 | 制造商:Intel 功能描述:ITANIUM PROCESSOR 1.6 GHZ - Boxed Product (Development Kits) |

| BX80551KG2800HUS L8MA | 制造商:Intel 功能描述:BOXED INTEL XEON PROCESSOR 2.80 GHZ, 4M CACHE, 800 MHZ FSB, PASSIVE, FC-MPGA |

| BX80551PE2666FNS L8ZH | 制造商:Intel 功能描述:MPU PENTIUM D 90NM 2.66GHZ 775PIN FCLGA4 - Boxed Product (Development Kits) |

| BX80552352 S L96P | 制造商:Intel 功能描述:MPU Celeron 制造商:Intel 功能描述:MPU Celeron? D Processor 352 65nm 3.2GHz 775-Pin FCLGA4 |

發(fā)布緊急采購,3分鐘左右您將得到回復。