- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄223348 > AM3505AZERA (TEXAS INSTRUMENTS INC) MICROPROCESSOR, PBGA484 PDF資料下載

參數(shù)資料

| 型號(hào): | AM3505AZERA |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | MICROPROCESSOR, PBGA484 |

| 封裝: | 23 X 23 MM, 1 MM PITCH, GREEN, PLASTIC, MO-151, BGA-494 |

| 文件頁(yè)數(shù): | 107/221頁(yè) |

| 文件大?。?/td> | 2153K |

| 代理商: | AM3505AZERA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)當(dāng)前第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)

i2cX_sda

i2cX_scl

STOP

START REPEAT

I1

I2

I3

I4

I6

I5

I7

030-094

SPRS550C

– OCTOBER 2009 – REVISED MARCH 2011

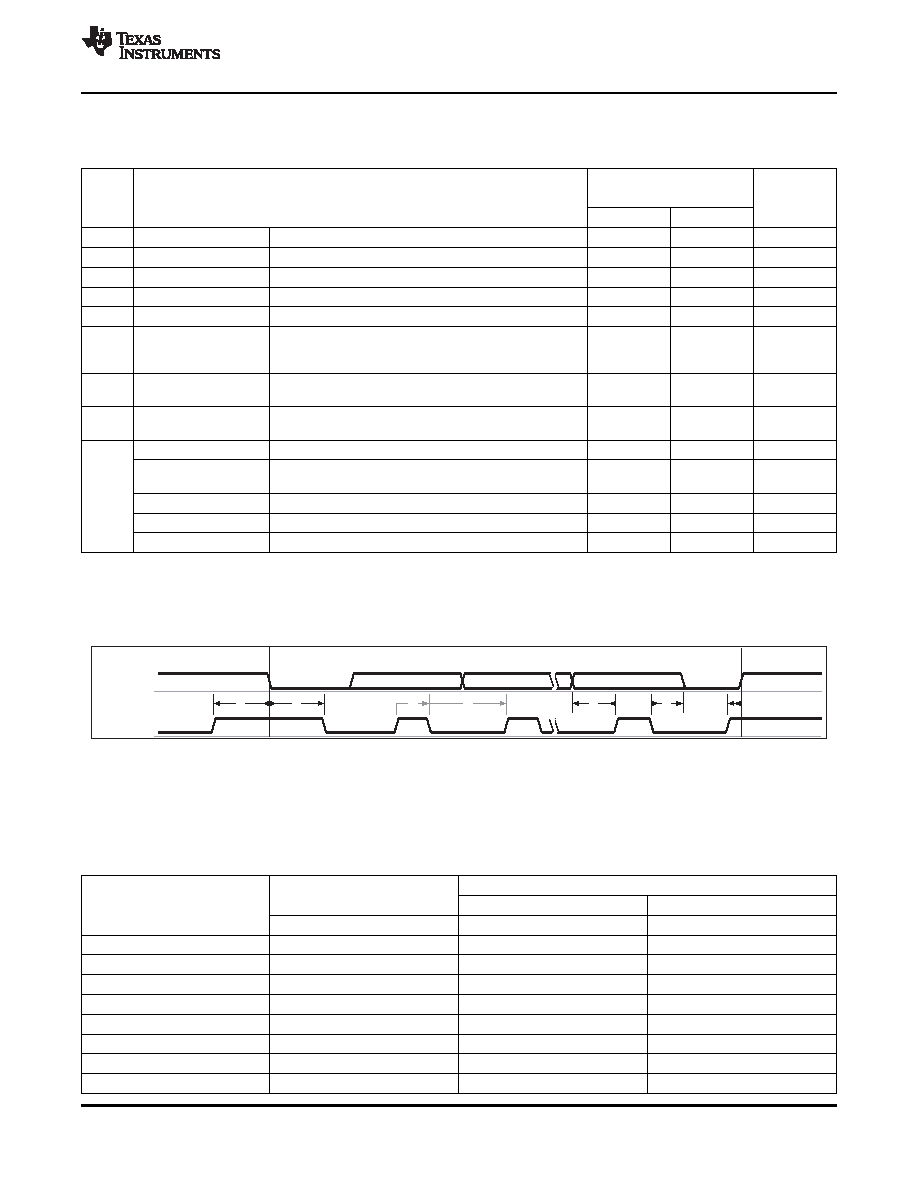

6.6.11.2 I2C High-Speed Mode

Table 6-127. I2C High-Speed Mode Timings(1) (2)

1.8V, 3.3V

NO.

PARAMETER

UNIT

MIN

MAX

fSCL

Clock frequency, i2cX_scl

3.4

MHz

I1

tw(SCLH)

Pulse duration, i2cX_scl high

60(3)

s

I2

tw(SCLL)

Pulse duration, i2cX_scl low

160(3)

s

I3

tsu(SDAV-SCLH)

Setup time, i2cX_sda valid before i2cX_scl active level

10

ns

I4

th(SCLHSDAV)

Hold time, i2cX_sda valid after i2cX_scl active level

70

s

I5

tsu(SDAL-SCLH)

Setup time, i2cX_scl high after i2cX_sda low

160

s

(for a START(4) condition or a repeated START

condition)

I6

th(SCLHSDAH)

Hold time, i2cX_sda low level after i2cX_scl high level

160

s

(STOP condition)

I7

th(SCLHRSTART)

Hold time, i2cX_sda low level after i2cX_scl high level

160

ns

(for a repeated START condition)

tR(SCL)

Rise time, i2cX_scl

10

40

ns

tR(SCL)

Rise time, i2cX_scl after a repeated START condition

10

80

ns

and after a bit acknowledge

tF(SCL)

Fall time, i2cX_scl

10

40

ns

tR(SDA)

Rise time, i2cX_sda

10

80

ns

tF(SDA)

Fall time, i2cX_sda

10

80

ns

(1)

In i2cX, X is equal to 1, 2, or 3.

(2)

The device provides (via the I2C bus) a hold time of at least 300 ns for the i2cx_sda signal (refer to the fall and rise time of i2cx_scl) to

bridge the undefined region of the falling edge of i2cx_scl.

(3)

HS-mode master devices generate a serial clock signal with a high to low ratio of 1 to 2. tw(SCLL) > 2 tw(SCLH).

(4)

After this time, the first clock is generated.

(1) HS-mode master devices generate a serial clock signal with a high-to-low ratio of 1 to 2. tw(SCLL) > 2 x tw(SCLH).

(2) In i2cX, X is equal to 1, 2, or 3.

(3) After this time, the first clock is generated.

Table 6-128. Correspondence Standard vs. TI Timing References

AM3517/05

STANDARD-I2C

S/F Mode

HS Mode

fSCL

FSCL

FSCLH

I1

tw(SCLH)

THIGH

I2

tw(SCLL)

TLOW

I3

tsu(SDAV-SCLH)

TSU;DAT

I4

th(SCLH-SDAV)

TSU;DAT

I5

tsu(SDAL-SCLH)

TSU;STA

I6

th(SCLH-SDAH)

THD;STA

I7

th(SCLH-RSTART)

TSU;STO

I8

tw(SDAH)

TBUF

Copyright

2009–2011, Texas Instruments Incorporated

TIMING REQUIREMENTS AND SWITCHING CHARACTERISTICS

195

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM3505AZER | MICROPROCESSOR, PBGA484 |

| AM41PDS3224DT11IT | SPECIALTY MEMORY CIRCUIT, PBGA73 |

| AM42-0040 | 5900 MHz - 6400 MHz RF/MICROWAVE NARROW BAND MEDIUM POWER AMPLIFIER |

| AM93L425SA/DMC | 1K X 1 STANDARD SRAM, 40 ns, CDIP16 |

| AM93L425A/LMC | 1K X 1 STANDARD SRAM, 55 ns, CQCC20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM3505AZERAC | 功能描述:微處理器 - MPU Sitara ARM Microproc RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| AM3505AZERC | 功能描述:微處理器 - MPU Sitara ARM Microproc RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:536 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| AM3505ZCN | 制造商:Texas Instruments 功能描述: |

| AM3505ZER | 制造商:Texas Instruments 功能描述: |

| AM350C-F04D-T | 制造商:SMC Corporation of America 功能描述:Mist sep G1/2 N/O autodrain + indicator |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。