- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373857 > AD14160L (Analog Devices, Inc.) Quad-SHARC DSP Multiprocessor Family PDF資料下載

參數(shù)資料

| 型號: | AD14160L |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Quad-SHARC DSP Multiprocessor Family |

| 中文描述: | 四SHARC處理器DSP的多處理器家族 |

| 文件頁數(shù): | 27/52頁 |

| 文件大小: | 1193K |

| 代理商: | AD14160L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

AD14160/AD14160L

–27–

REV. A

40 MHz–5 V

40 MHz–3.3 V

Min

Parameter

Min

Max

Max

Units

Timing Requirements:

t

STSCK

t

HTSCK

SBTS

Setup Before CLKIN

SBTS

Hold Before CLKIN

12 + DT/2

12 + DT/2

ns

ns

6 + DT/2

6 + DT/2

Switching Characteristics:

t

MIENA

t

MIENS

t

MIENHG

t

MITRA

t

MITRS

t

MITRHG

t

DATEN

t

DATTR

t

ACKEN

t

ACKTR

t

ADCEN

t

ADCTR

t

MTRHBG

t

MENHBG

Address/Select Enable After CLKIN

Strobes Enable After CLKIN

1

HBG

Enable After CLKIN

Address/Select Disable After CLKIN

Strobes Disable After CLKIN

1

HBG

Disable After CLKIN

Data Enable After CLKIN

2

Data Disable After CLKIN

2

ACK Enable After CLKIN

2

ACK Disable After CLKIN

2

ADRCLK Enable After CLKIN

ADRCLK Disable After CLKIN

Memory Interface Disable Before

HBG

Low

3

Memory Interface Enable After

HBG

High

3

–1.5 – DT/8

–1.5 – DT/8

–1.5 – DT/8

–1.25 – DT/8

–1.5 – DT/8

–1.5 – DT/8

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

1 – DT/4

2.5 – DT/4

2.5 – DT/4

1 – DT/4

2.5 – DT/4

2.5 – DT/4

9 + 5DT/16

0 – DT/8

7.5 + DT/4

–1 – DT/8

–2 – DT/8

9 + 5DT/16

0 – DT/8

7.5 + DT/4

–1 – DT/8

–2 – DT/8

8 – DT/8

8 – DT/8

7 – DT/8

7 – DT/8

8.5 – DT/4

8.5 – DT/4

–0.5 + DT/8

18.5 + DT

–0.5 + DT/8

18.5 + DT

NOTES

1

Strobes =

RD

,

WR

,

SW

, PAGE,

DMAG

.

2

In addition to bus master transition cycles, these specs also apply to bus master and bus slave synchronous read/write.

3

Memory Interface = Address,

RD

,

WR

,

MS

x,

SW

,

HBG

, PAGE,

DMAGx

,

BMS

(in EPROM boot mode).

CLKIN

ACK

MEMORY

INTERFACE

t

MENHBG

t

MTRHBG

HBG

MEMORY INTERFACE = ADDRESS,

RD

,

WR

,

MS

x,

SW

,

HBG

, PAGE,

DMAG

x.

BMS

(IN EPROM BOOT MODE)

t

MITRA,

t

MITRS,

t

MITRHG

t

STSCK

t

HTSCK

t

DATTR

t

DATEN

t

ACKTR

t

ACKEN

t

ADCTR

t

ADCEN

ADRCLK

DATA

t

MIENA,

t

MIENS,

t

MIENHG

MEMORY

INTERFACE

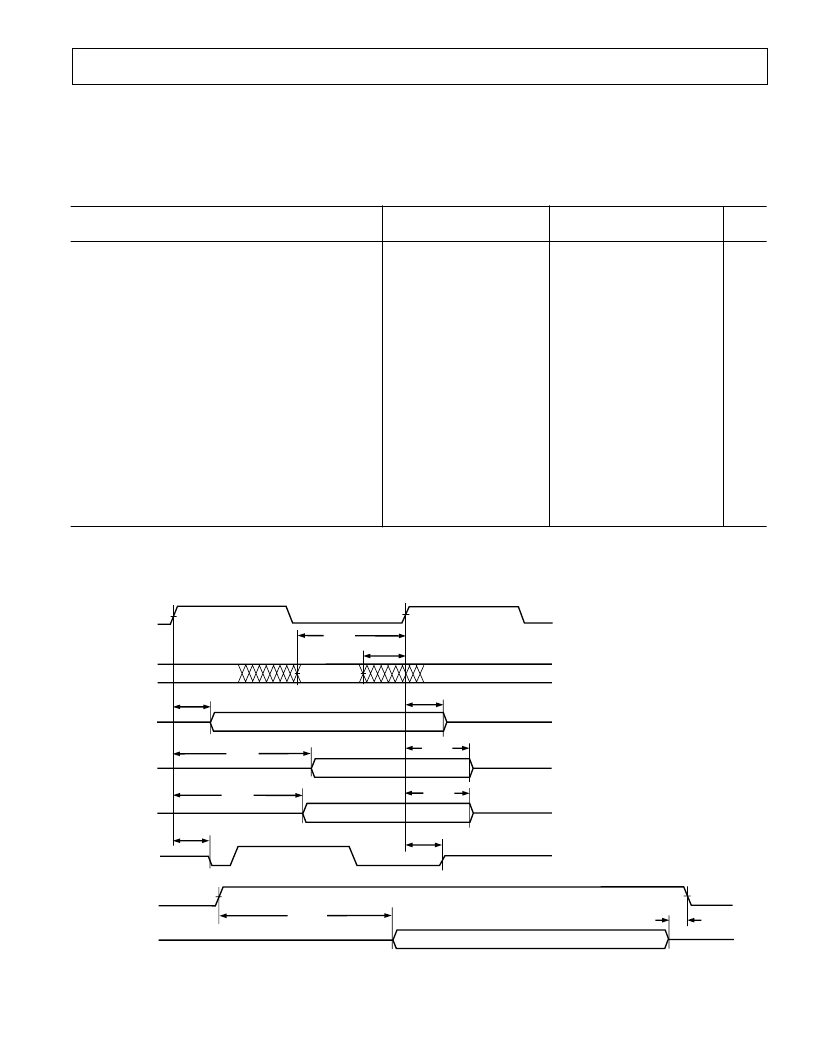

Figure 20. Three-State Timing

Three-State Timing—Bus Master, Bus Slave,

HBR

,

SBTS

These specifications show how the memory interface is disabled

(stops driving) or enabled (resumes driving) relative to CLKIN

and the

SBTS

pin. This timing is applicable to bus master tran-

sition cycles (BTC) and host transition cycles (HTC) as well as

the

SBTS

pin.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD14160LBB-4 | ECONOLINE: RD & RC - Dual Output from a Single Input Rail- 1kVDC & 2kVDC Isolation- Power Sharing on Output- Custom Solutions Available- UL94V-0 Package Material- Efficiency to 86% |

| AD14160LKB-4 | Quad-SHARC DSP Multiprocessor Family |

| AD1555-AD1556 | 24-Bit ADC WITH LOW NOISE PGA |

| AD1555AP | 24-Bit ADC WITH LOW NOISE PGA |

| AD1555APRL | 24-Bit ADC WITH LOW NOISE PGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD14160LBB-4 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Quad-SHARC DSP Multiprocessor Family |

| AD14160LKB-4 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD142 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRANSISTOR | BJT | PNP | 80V V(BR)CEO | 10A I(C) | TO-3 |

| AD143 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRANSISTOR | BJT | PNP | 40V V(BR)CEO | 10A I(C) | TO-3 |

| AD-1432-ACD10FT-LPG-HOSE | 制造商:TE Connectivity 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。