- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373857 > AD14160BB-4 (ANALOG DEVICES INC) Quad-SHARC DSP Multiprocessor Family PDF資料下載

參數(shù)資料

| 型號: | AD14160BB-4 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | Quad-SHARC DSP Multiprocessor Family |

| 中文描述: | 48-BIT, 40 MHz, OTHER DSP, CBGA452 |

| 封裝: | CERAMIC, BGA-452 |

| 文件頁數(shù): | 18/52頁 |

| 文件大小: | 1193K |

| 代理商: | AD14160BB-4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

AD14160/AD14160L

–18–

REV. A

40 MHz–5 V

40 MHz–3.3 V

Min

Parameter

Min

Max

Max

Units

Timing Requirements:

t

DAD

t

DRLD

t

HDA

t

HDRH

t

DAAK

t

DSAK

Address, Selects Delay to Data Valid

1, 2

RD

Low to Data Valid

1

Data Hold from Address

3

Data Hold from

RD

High

3

ACK Delay from Address

2, 4

ACK Delay from

RD

Low

4

17 + DT + W

11 + 5DT/8 + W

17 + DT + W

11 + 5DT/8 + W

ns

ns

ns

ns

ns

ns

1.5

3

1.5

3

13 + 7DT/8 + W

7 + DT/2 + W

13 + 7DT/8 + W

7 + DT/2 + W

Switching Characteristics:

t

DRHA

t

DARL

t

RW

t

RWR

t

SADADC

Address Hold After

RD

High

Address to

RD

Low

2

RD

Pulsewidth

RD

High to

WR

,

RD

,

DMAGx

Low

Address Setup Before ADRCLK High

2

–1 + H

1 + 3DT/8

12.5 + 5DT/8 + W

7.5 + 3DT/8 + HI

–0.5 + DT/4

–1 + H

1 + 3DT/8

12.5 + 5DT/8 + W

7.5 + 3DT/8 + HI

–0.5 + DT/4

ns

ns

ns

ns

ns

W = (number of wait states specified in WAIT register)

×

t

CK.

HI = t

CK

(if an address hold cycle or bus idle cycle occurs, as specified in WAIT register; otherwise HI = 0).

H = t

CK

(if an address hold cycle occurs as specified in WAIT register; otherwise H = 0).

NOTES

1

Data Delay/Setup: User must meet t

or t

or synchronous spec t

SSDATI

.

2

For

MS

x,

SW

,

BMS

, the falling edge is referenced.

3

Data Hold: User must meet t

HDA

or t

HDRH

or synchronous spec t

HDATI

. See System Hold Time Calculation under Test Conditions for the calculation of hold times

given capacitive and dc loads.

4

ACK Delay/Setup: User must meet t

DSAK

or t

DAAK

or synchronous specification t

SACKC

.

WR,

DMAG

ACK

DATA

RD

ADDRESS

MS

x,

SW

BMS

t

DARL

t

RW

t

DAD

t

SADADC

t

DAAK

t

HDRH

t

HDA

t

RWR

t

DRLD

ADRCLK

(OUT)

t

DRHA

t

DSAK

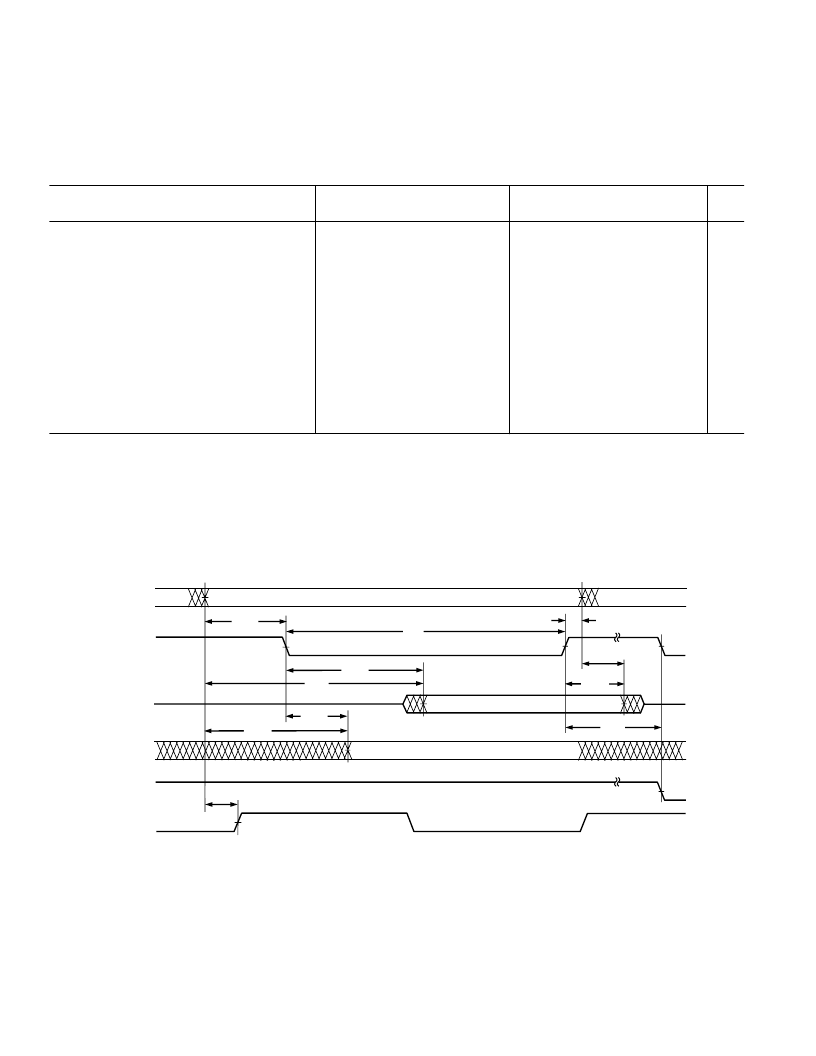

Figure 14. Memory Read—Bus Master

Memory Read—Bus Master

Use these specifications for asynchronous interfacing to memo-

ries (and memory-mapped peripherals) without reference to

CLKIN. These specifications apply when the AD14160/

AD14160L is the bus master accessing external memory space.

These switching characteristics also apply for bus master syn-

chronous read/write timing (see Synchronous Read/Write—Bus

Master below). If these timing requirements are met, the syn-

chronous read/write timing can be ignored (and vice versa).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD14160L | Quad-SHARC DSP Multiprocessor Family |

| AD14160LBB-4 | ECONOLINE: RD & RC - Dual Output from a Single Input Rail- 1kVDC & 2kVDC Isolation- Power Sharing on Output- Custom Solutions Available- UL94V-0 Package Material- Efficiency to 86% |

| AD14160LKB-4 | Quad-SHARC DSP Multiprocessor Family |

| AD1555-AD1556 | 24-Bit ADC WITH LOW NOISE PGA |

| AD1555AP | 24-Bit ADC WITH LOW NOISE PGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD14160KB-4 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD14160L | 制造商:AD 制造商全稱:Analog Devices 功能描述:Quad-SHARC DSP Multiprocessor Family |

| AD14160LBB-4 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Quad-SHARC DSP Multiprocessor Family |

| AD14160LKB-4 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD142 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRANSISTOR | BJT | PNP | 80V V(BR)CEO | 10A I(C) | TO-3 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。