- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄294088 > 70824L35PFI (INTEGRATED DEVICE TECHNOLOGY INC) 4K X 16 STANDARD SRAM, 35 ns, PQFP80 PDF資料下載

參數(shù)資料

| 型號(hào): | 70824L35PFI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | SRAM |

| 英文描述: | 4K X 16 STANDARD SRAM, 35 ns, PQFP80 |

| 封裝: | TQFP-80 |

| 文件頁(yè)數(shù): | 15/21頁(yè) |

| 文件大?。?/td> | 191K |

| 代理商: | 70824L35PFI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

6.42

IDT70824S/L

High-Speed 4K x 16 Sequential Access Random Access Memory

Military and Commercial Temperature Ranges

3

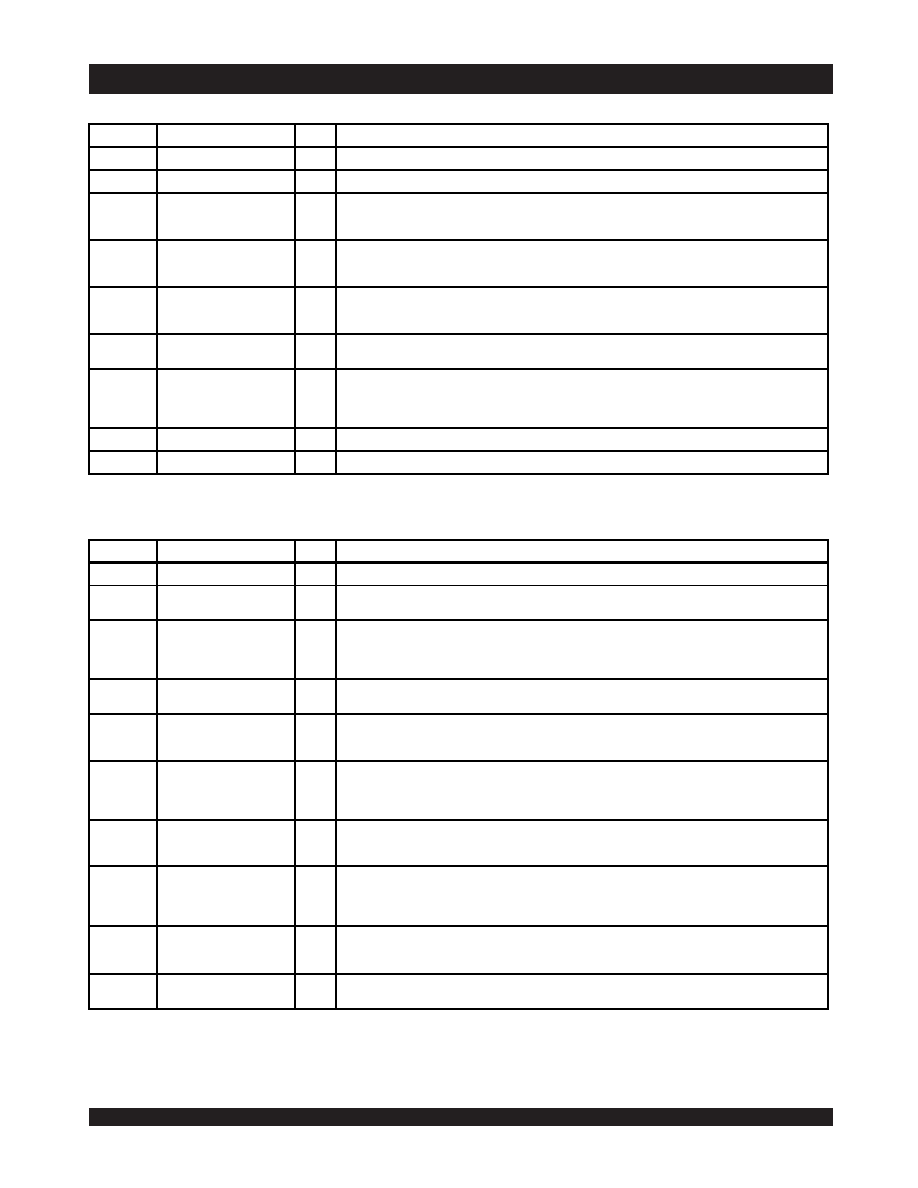

Pin Descriptions: Random Access Port(1)

Pin Descriptions: Sequential Access Port(1)

NOTE:

1. "I/O" is bidirectional Input and Output. "I" is Input and "O" is Output.

SYMBOL

NAME

I/O

DESCRIPTION

A0-A11

Address Lines

I

Address inputs to access the 4096-word (16-Bit) memory array.

I/O0-I/O15

Inputs/Outputs

I

Random access data inputs/outputs for 16-Bit wide data.

CE

Chip Enable

I

When

CE is LOW, the random access port is enabled. When CE is HIGH, the random access port is disabled

into power-down mode and the I/O outputs are in the High-impedance state. All data is retained during

CE =

VIH, unless it is altered by the sequential port

CE and CMD may not be LOW at the same time.

CMD

Control Register Enable

I

When

CMD is LOW, address lines A0-A2, R/W, and inputs and outputs I/O0-I/O12, are used to access the

control register, the flag register and the start and end of buffer registers.

CMD and CE may not be LOW at the

same time.

R/

W

Read/Write Enable

I

If

CE is LOW and CMD is HIGH, data is written into the array when R/W is LOW and read out of the array when

R/

W is HIGH. If CE is HIGH and CMD is LOW, R/W is used to access the buffer command registers. CE and

CMD may not be LOW at the same time.

OE

Output Enable

I

When

OE is LOW and R/W is HIGH, I/O0-I/O15 outputs are enabled. When OE is HIGH, the I/O outputs are in

the High-impedance state.

LB, UB

Lower Byte, Upper Byte

Enables

I

When

LB is LOW, I/O0-I/O7 are accessible for read and write operations. When LB is HIGH, I/O0-I/O7 are tri-

stated and blocked during read and write operations.

UB controls access for I/O8-I/O15 in the same manner and

is asynchronous

from

LB.

VCC

Power Supply

I

Seven +5 power supply pins. All VCC pins must be connected to the same +5V VCC supply.

GND

Ground

I

Ten ground pins. All ground pins must be connected to the same ground supply.

3099 tbl 01

SYMBOL

NAME

I/O

DESCRIPTION

SI/O0-15

Inputs/Outputs

I/O

Sequential data inputs/outputs for 16-bit wide data.

SCLK

Clock

I

SI/O0-SI/O15,

SCE, SR/W, and SLD are registered on the LOW-to-HIGH transition of SCLK. Also, the sequential

access port address pointer increments by 1 on e ach LOW-TO-HIGH transition of SCLK when

CNTEN is LOW.

SCE

Chip Enable

I

When

SCE is LOW, the sequential access port is enabled on the LOW-to-HIGH transition of SCLK. When SCE

is HIGH, the sequential access port is disabled into powered-d own mode on the LOW-to-HIGH transition of

SCLK, and the SI/O outputs are in the High-impedance state. All data is retained , unless altered by the random

access port.

CNTEN

Counter Enable

I

When

CNTEN is LOW, the address pointer increments on the LOW-to-HIGH transition of SCLK. This function is

independent of

CE.

SR/

W

Read/Write Enable

I

When SR/

W and SCE are LOW, a write cycle is initiated on the LOW-to-HIGH transition of SCLK. When SR/ W is

HIGH, and

SCE and SOE are LOW, a read cycle is initiated on the LOW-to-HIGH transition of SCLK. Termination

o f a write cycle is done on the LOW-to -HIGH transition of SCLK if SR/W or

SCE is HIGH.

SLD

Address Pointer Load Control

I

When

SLD is sampled LOW, there is an internal delay of one cycle before the address pointer changes. When

SLD is LOW, data on the inputs SI/O0-SI/O11 is loaded into a data-in register on the LOW-to-HIGH transition of

SCLK. On the Cycle following

SLD, the address pointer charges to the address location contained in the data-

in register.

SSTRT1 and SSTRT2 may not be LOW while SLD is LOW or during the cycle following SLD.

SSTRT1,

SSTRT2

Load Start of Address

Register

I

When

SSTRT1 or SSTRT2 is LOW, the start of address register #1 or #2 is loaded into the address pointer on

the LOW-to-HIGH transition of SCLK. The start addresses are stored in internal registers.

SSTRT1 and SSTRT2

may not be LOW while

SLD is LOW or during the cycle following SLD.

EOB1,

EOB2

End of Buffer Flag

O

EOB1 or EOB2 is output low when the address pointer is incremented to match the address stored in the end

of buffer registers. The flags can be cleared by either asserting

RST LOW or by writing zero into Bit 0 and/or

Bit 1 of the control registe r at address 101.

EOB1 and EOB2 are dependent on separate internal registers, and

therefore separate match addresses.

SOE

Output Enable

I

SOE controls the data outputs and is independent of SCLK. When SOE is LOW, output buffers and the

se quentially ad dressed data is output. When

SOE is HIGH, the SI/O output bus is in the High-impedance state.

SOE is asynchronous to SCLK.

RST

Reset

I

When

RST is LOW, all internal registers are set to their default state, the address pointer is set to zero and the

EOB1 and EOB2 flags are set HIGH. RST is asynchronous to SCLK.

3099 tbl 02

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 709176001422006 | PCB CONNECTOR |

| 709176001432006 | PCB CONNECTOR |

| 709176001501006 | PCB CONNECTOR |

| 709176001511006 | PCB CONNECTOR |

| 709176001522006 | PCB CONNECTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 70824S20PF | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Async Dual 5V 64K-Bit 4K x 16 20ns 80-Pin TQFP Tray |

| 70824S25PF | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Async Dual 5V 64K-Bit 4K x 16 25ns 80-Pin TQFP Tray |

| 70825 | 制造商:Gems Sensors & Controls 功能描述:Switches Flow Port Size:1/4" 制造商:Gems Sensors & Controls 功能描述:FLOW SENSOR, 1.5GPM, 69BAR, 1/4" NPT; Pressure Max:69bar; Accuracy %:15%; Port Size:6.35mm; Accuracy:+/-15%; Body Material:Brass; Circuitry:SPST; Connection Size:1/4"; Features:Normally Open at No Flow; Flow Measuring Range:- ;RoHS Compliant: Yes |

| 708250 | 功能描述:固定接線端子 VDFK 4 RoHS:否 制造商:Phoenix Contact 產(chǎn)品:Fixed Terminal Blocks 類型:Wire to Board 節(jié)距:5.08 mm 位置/觸點(diǎn)數(shù)量:2 線規(guī)量程:26-16 電流額定值:13.5 A 電壓額定值:250 V 安裝風(fēng)格:Through Hole 安裝角:Straight 端接類型:Screw 觸點(diǎn)電鍍: |

| 7082534 | 制造商:WIKA INSTRUMENTS 功能描述:Sensor; A-AI-1 Loop Pwrd Ind. for S-10, S-11, A-10 w/DIN 43650, 4-20mA, 2 Wire |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。