- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄1887 > 5AGXMB3G6F31C6NES (Altera)IC ARRIA V FPGA 362K 896FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | 5AGXMB3G6F31C6NES |

| 廠商: | Altera |

| 文件頁(yè)數(shù): | 9/124頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC ARRIA V FPGA 362K 896FBGA |

| 標(biāo)準(zhǔn)包裝: | 3 |

| 系列: | Arria V GX |

| LAB/CLB數(shù): | 17110 |

| 邏輯元件/單元數(shù): | 362730 |

| RAM 位總計(jì): | 2148352 |

| 輸入/輸出數(shù): | 384 |

| 電源電壓: | 1.07 V ~ 1.13 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 896-BGA |

| 供應(yīng)商設(shè)備封裝: | 896-FBGA(31x31) |

| 其它名稱: | 544-2735 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)

Page 34

Switching Characteristics

Arria V GZ Device Datasheet

February 2014

Altera Corporation

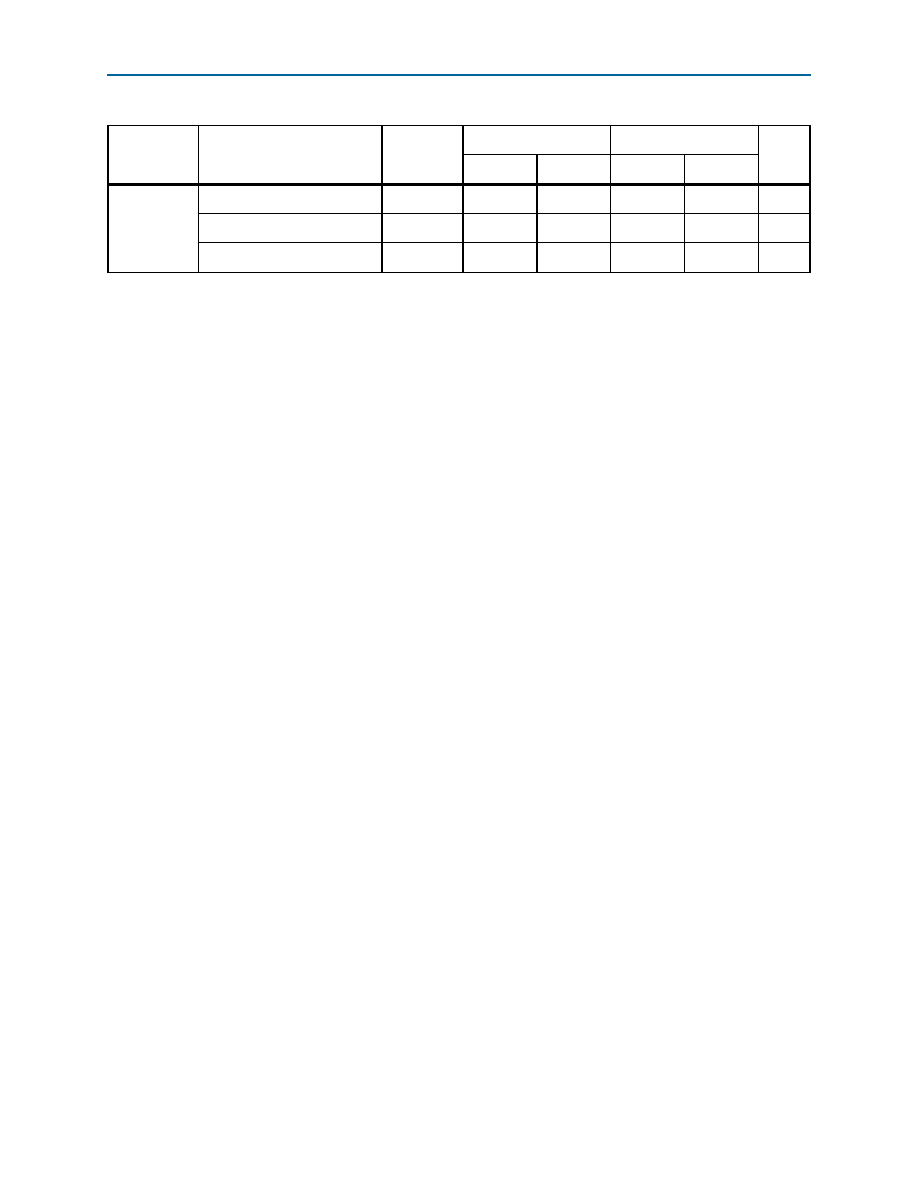

PHY Clock

Clock period jitter

t

JIT(per)

–30

30

–35

35

ps

Cycle-to-cycle period jitter

t

JIT(cc)

–60

60

–70

70

ps

Duty cycle jitter

t

JIT(duty)

–45

45

–56

56

ps

Notes to Table 39:

(1) The clock jitter specification applies to the memory output clock pins generated using differential signal-splitter and DDIO circuits clocked by

a PLL output routed on a PHY, regional, or global clock network as specified. Altera recommends using PHY clock networks whenever possible.

(2) The clock jitter specification applies to the memory output clock pins clocked by an integer PLL.

(3) The memory output clock jitter is applicable when an input jitter of 30 ps peak-to-peak is applied with bit error rate (BER) -12, equivalent to 14

sigma.

Table 39. Memory Output Clock Jitter Specification for Arria V GZ Devices (1), (2), (3) (Part 2 of 2)

Clock

Network

Parameter

Symbol

C3, I3L

C4, I4

Unit

Min

Max

Min

Max

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5CGXFC7D7F31C8NES | IC CYCLONE V FPGA 150K 896-FBGA |

| 668-0003-C | IC CPU RABBIT2000 30MHZ 100PQFP |

| 668-0011 | IC MPU RABIT3000A 55.5MHZ128LQFP |

| 6PAIC3106IRGZRQ1 | IC AUDIO CODEC STEREO 48-QFN |

| 70001851 | DEVICE SERVER 1PORT SRL-ETHERNET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5AGXMB3G6F35C6N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Arria V GX 13688 LABs 544 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| 5AGXMB3G6F40C6N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Arria V GX 13688 LABs 704 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| 5AGXMB5G4F35C4N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Arria V GX 15849 LABs 544 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| 5AGXMB5G4F35C5G | 功能描述:1152-PIN FBGA 制造商:altera 系列:Arria V GX 零件狀態(tài):在售 LAB/CLB 數(shù):19811 邏輯元件/單元數(shù):420000 總 RAM 位數(shù):23625728 I/O 數(shù):544 電壓 - 電源:1.07 V ~ 1.13 V 工作溫度:0°C ~ 85°C(TJ) 標(biāo)準(zhǔn)包裝:24 |

| 5AGXMB5G4F35C5N | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 FPGA - Arria V GX 15849 LABs 544 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。