- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄157280 > 5962F9855202QXA 32-BIT, 16 MHz, RISC MICROCONTROLLER, CPGA144 PDF資料下載

參數(shù)資料

| 型號: | 5962F9855202QXA |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 16 MHz, RISC MICROCONTROLLER, CPGA144 |

| 封裝: | CERAMIC, PGA-144 |

| 文件頁數(shù): | 45/64頁 |

| 文件大小: | 1464K |

| 代理商: | 5962F9855202QXA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

5

The UT69R000 begins operation by first generating an address

on the instruction port; valid data (instruction) is then latched

into the Primary Instruction Register (PIR). After the machine

stores the instruction in the PIR, the machine begins execution

of the instruction in the Instruction Register (IR). If the present

instruction in the IR requires only internal processing, the

machine does not exercise the data bus. If the machine needs

additional data to complete the instruction the machine begins

arbitration for the data port.

Data port arbitration begins with the machine asserting the Bus

Request (BRQ) signal. The machine samples the Bus Grant

(BGNT) and Bus Busy (BUSY) signals on the falling edge of

the clock (OSCIN). When the machine detects that the previous

bus controller has relinquished control of the bus, the machine

generates a Bus Grant Acknowledge (BGACK) signal

signifying that it has taken control of the bus (i.e., data port).

After the UT69R000 takes control of the bus, it generates valid

address and data information. If the machine is interfacing to

slow memory or other peripheral devices that require long

memory-access times, the Data Transfer Acknowledge

(DTACK) signal extends the memory cycle time. By holding

off the assertion of DTACK, the slow device lengthens the

memory cycle until it can provide data for the machine.

The UT69R000 controls the vectoring and prioritizing of

interrupt service. Internal logic selects one of 15 interrupt

vectors, each interrupt vector is allocated four memory

locations. Use the four memory locations to store return from

interrupt service address information along with the interrupt

service routine’s location. The UT69R000 controls prioritizing

of coincident interrupts.

Perform UART control and maintenance via input/output

commands OTR and INR. These commands allow the

programmer to read UART status, and error information, as

well as upload and download information to the receive and

transmit buffers respectively.

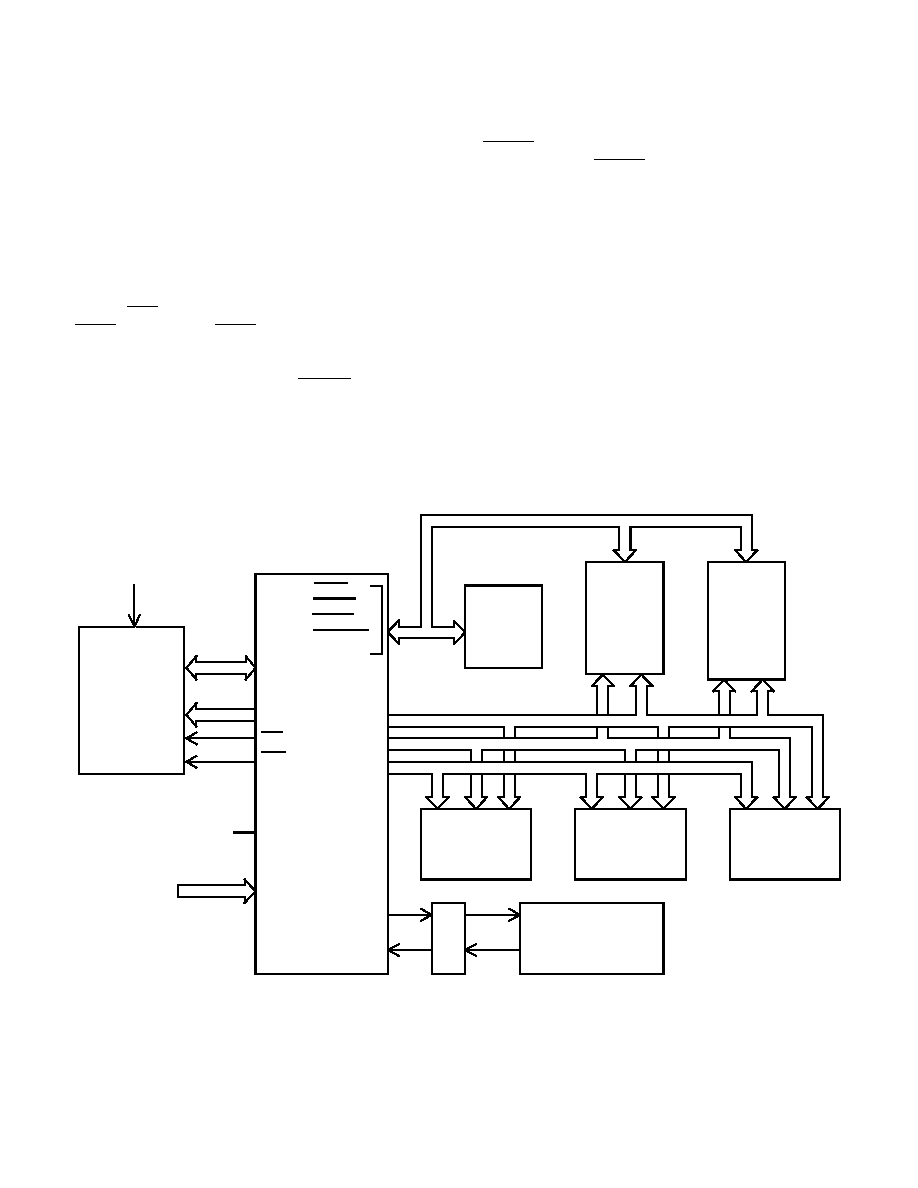

Figure 4 shows an example of a system configuration.

INSTRUCTION

DATA

INSTRUCTION

ADD

16

20

NUI3

USER-

DEFINED

SYSTEM

INTERRUPTS

8

UART

I/F

X

C

V

R

GENERAL

PURPOSE

MEMORY

I/O

DEVICE #1

I/O

DEVICE #2

BUS

ARBITER

DMA

DEVICE

#1

1553

I/F

DMA

DEVICE

#2

OP ADD

OP DATA

CONTROL

16

6

Figure 4. The UT69R000 Example System Configuration

4

UT69R000

INSTRUCTION MEMORY

CAN ONLY BE ACCESSED

BY THE UT69R000

INSTRUCTION

MEMORY

1M X 16

INTERNALLY

PULLED LOW

SERIAL I/O

BUSY

BGACK

BRQ

BGNT

OE

WE

(MAX)

相關PDF資料 |

PDF描述 |

|---|---|

| 5962G9855201QXX | 32-BIT, 12 MHz, RISC MICROCONTROLLER, CPGA144 |

| 5962G9855202VXA | 32-BIT, 16 MHz, RISC MICROCONTROLLER, CPGA144 |

| 5962G9855202VXX | 32-BIT, 16 MHz, RISC MICROCONTROLLER, CPGA144 |

| 5962H9855201VXC | 32-BIT, 12 MHz, RISC MICROCONTROLLER, CPGA144 |

| 5962H9855202QXX | 32-BIT, 16 MHz, RISC MICROCONTROLLER, CPGA144 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 5962F9861301VCC | 制造商:Intersil Corporation 功能描述: |

| 5962F9861301VHA | 制造商:Intersil Corporation 功能描述:- Bulk |

| 5962F9861301VXC | 制造商:Intersil Corporation 功能描述: |

| 5962F9865102QYA | 制造商:STMicroelectronics 功能描述:EIA-644LINE DRIVERQUADFLAT16, SOLDER DIP - Bulk |

| 5962F9865102QYC | 制造商:STMicroelectronics 功能描述:EIA-644LINE DRIVERQUADFLAT16, GOLD - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。