- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373783 > ZL30121GGG (ZARLINK SEMICONDUCTOR INC) SONET/SDH Low Jitter System Synchronizer PDF資料下載

參數(shù)資料

| 型號: | ZL30121GGG |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | SONET/SDH Low Jitter System Synchronizer |

| 中文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA100 |

| 封裝: | 9 X 9 MM, 0.80 MM PITCH, CABGA-100 |

| 文件頁數(shù): | 24/30頁 |

| 文件大小: | 326K |

| 代理商: | ZL30121GGG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁

ZL30121

Data Sheet

24

Zarlink Semiconductor Inc.

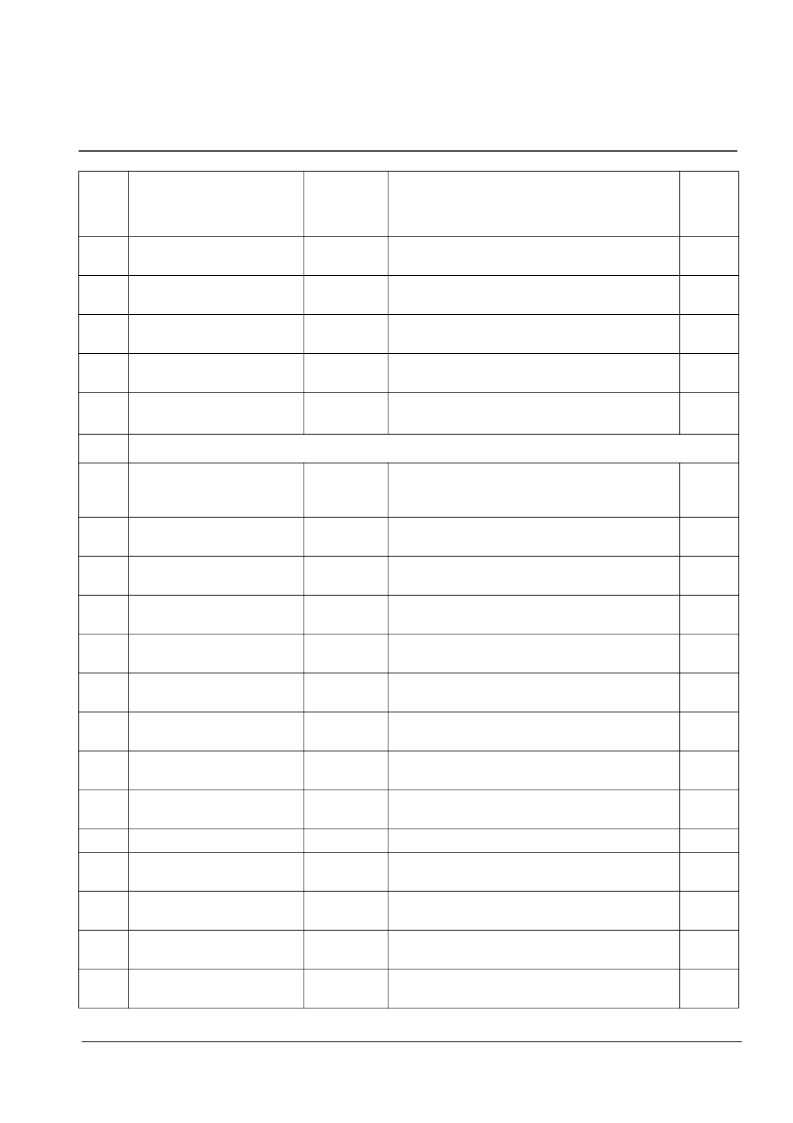

31

dpll2_ref_pri_ctrl_0

10

Control register for the ref0 and ref1 priority

values

R/W

32

dpll2_ref_pri_ctrl_1

32

Control register for the ref2 and ref3 priority

values

R/W

33

dpll2_ref_pri_ctrl_2

54

Control register for the ref4 and re5 priority

values

R/W

34

dpll2_ref_pri_ctrl_3

76

Control register for the ref6 and ref7 priority

values

R/W

35

dpll2_lock_holdover_status

04

DPLL2 lock and holdover status register

R

P0 Configuration Registers

36

p0_enable

8F

Control register to enable p0_clk0, p0_clk1,

p0_fp0, p0_fp1, the P0 synthesizer and select

the source

R/W

37

p0_run

0F

Control register to generate p0_clk0, p0_clk1,

p0_fp0 and p0_fp1

R/W

38

p0_freq_0

00

Control register for the [7:0] bits of the N of

N*8k clk0

R/W

39

p0_freq_1

01

Control register for the [13:8] bits of the N of

N*8k clk0

R/W

3A

p0_clk0_offset90

00

Control register for the p0_clk0 phase position

coarse tuning

R/W

3B

p0_clk1_div

3E

Control register for the p0_clk1 frequency

selection

R/W

3C

p0_clk1_offset90

00

Control register for the p0_clk1 phase position

coarse tuning

R/W

3D

p0_offset_fine

00

Control register for the output/output phase

alignment fine tuning for p0 path

R/W

3E

p0_fp0_freq

05

Control register to select the p0_fp0 frame

pulse frequency

R/W

3F

p0_fp0_type

83

Control register to select fp0 type

R/W

40

p0_fp0_fine_offset_0

00

Bits [7:0] of the programmable frame pulse

phase offset in multiples of 1/262.14 MHz

R/W

41

p0_fp0_fine_offset_1

00

Bits [15:8] of the programmable frame pulse

phase offset in multiples of 1/262.14 MHz

R/W

42

p0_fp0_coarse_offset

00

Programmable frame pulse phase offset in

multiples of 8 kHz cycles

R/W

43

p0_fp1_freq

05

Control register to select p0_fp1 frame pulse

frequency

R/W

Addr

(Hex)

Register

Name

Reset

Value

(Hex)

Description

Type

Table 5 - Register Map (continued)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL30122 | SONET/SDH Low Jitter Line Card Synchronizer |

| ZL30122GGG | SONET/SDH Low Jitter Line Card Synchronizer |

| ZL30406 | SONET/SDH Clock Multiplier PLL |

| ZL30406QGC | Digital Multimeter Clamp Battery Size Code:9V; Current Measuring Range:40.00/400.0A; Current Setting AC:400A; Current Setting DC:400A; Resistance Measuring Range:400 Ohm, 4000 - 40 - 400 kOhm; Voltage Measuring Range AC:600 V RoHS Compliant: NA |

| ZL30406QGC1 | SONET/SDH Clock Multiplier PLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL30121GGG2 | 制造商:Microsemi Corporation 功能描述:PB FREE LOW JITTER SYSTEM SYNCHRONIZER |

| ZL30121GGG2V2 | 制造商:Microsemi Corporation 功能描述:REV 2 PB FREE LOW JITTER SYSTEM SYNCHRO 制造商:Microsemi Corporation 功能描述:REV 2 PB FREE LOW JITTER SYSTEM SYNCHRO - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SONET/SDH SYNCH 100CABGA 制造商:Microsemi Corporation 功能描述:IC SONET/SDH SYNCH 100CABGA |

| ZL30121GGGV2 | 制造商:Microsemi Corporation 功能描述:LOW JITTER SYSTEM SYNCHRONIZER 制造商:Microsemi Corporation 功能描述:REV 2 LOW JITTER SYSTEM SYNCHRONIZER - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SONET/SDH SYNCH 100CABGA 制造商:Microsemi Corporation 功能描述:IC SONET/SDH SYNCH 100CABGA |

| ZL30122 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:SONET/SDH Low Jitter Line Card Synchronizer |

| ZL30122GGG | 制造商:Microsemi Corporation 功能描述:LOW JITTER SYSTEM SYNCHRONIZER 制造商:Microsemi Corporation 功能描述:SONET/SDH LOW JITTER LINE CARD SYNCHRONIZER 64CABGA - Trays 制造商:Microsemi Corporation 功能描述:IC SONET/SDH SYNCH 64CABGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。