- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373783 > ZL30121GGG (ZARLINK SEMICONDUCTOR INC) SONET/SDH Low Jitter System Synchronizer PDF資料下載

參數(shù)資料

| 型號: | ZL30121GGG |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | SONET/SDH Low Jitter System Synchronizer |

| 中文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA100 |

| 封裝: | 9 X 9 MM, 0.80 MM PITCH, CABGA-100 |

| 文件頁數(shù): | 18/30頁 |

| 文件大小: | 326K |

| 代理商: | ZL30121GGG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

ZL30121

Data Sheet

18

Zarlink Semiconductor Inc.

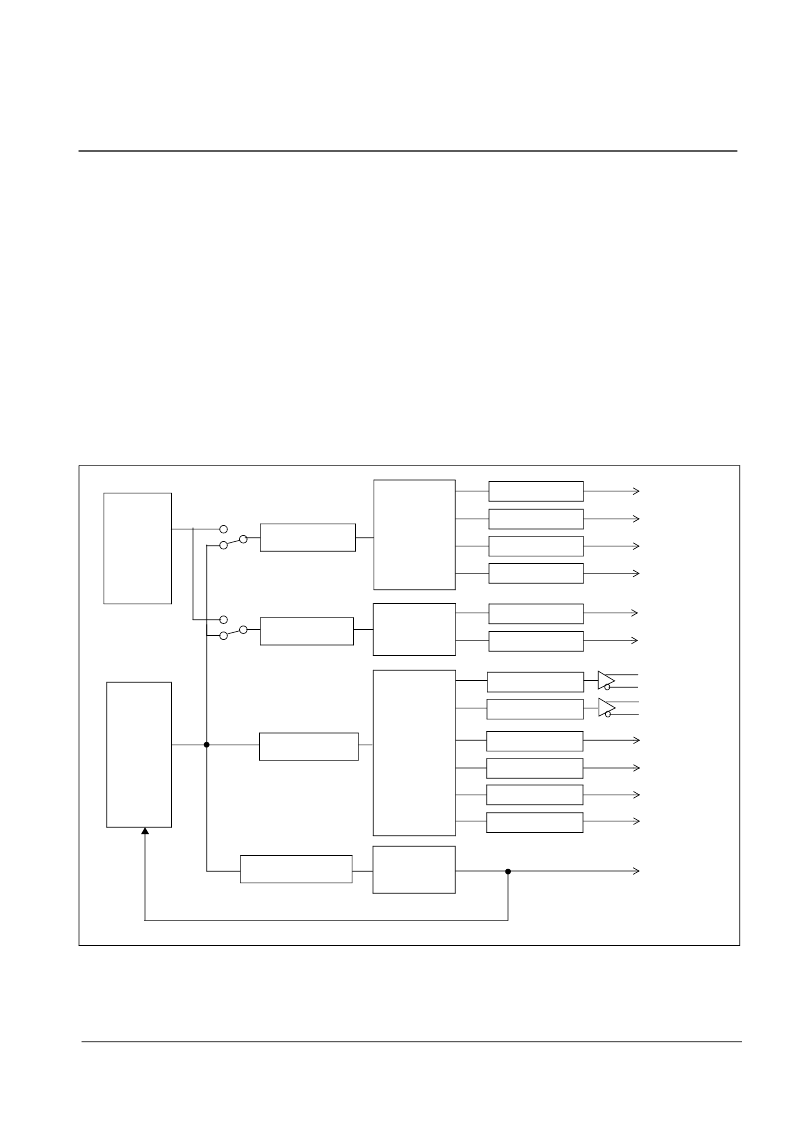

1.6 Configurable Input-to-Output and Output-to-Output Delays

The ZL30121 allows programmable static delay compensation for controlling input-to-output and output-to-output

delays of its clocks and frame pulses.

All of the output synthesizers (SONET/SDH, P0, P1, Feedback) locked to DPLL1 can be configured to lead or lag

the selected input reference clock using the

DPLL1 Fine Delay

. The delay is programmed in steps of 119.2 ps with

a range of -128 to +127 steps giving a total delay adjustment in the range of -15.26 ns to +15.14 ns. Negative

values delay the output clock, positive values advance the output clock. Synthesizers that are locked to DPLL2 are

unaffected by this delay adjustment.

In addition to the fine delay introduced in the DPLL1 path, the SONET/SDH, P0, and P1 synthesizers have the

ability to add their own fine delay adjustments using the

,

P1 Fine Delay

, and

SDH Fine Delay

.

These delays are also programmable in steps of 119.2 ps with a range of -128 to +127 steps.

In addition to these delays, the single-ended output clocks of the SONET/SDH, P0, and P1 synthesizers can be

independently offset by 90, 180 and 270 degrees using the

Coarse Delay

, and the SONET/SDH differential outputs

can be independently delayed by -1.6 ns, 0 ns, +1.6 ns or +3.2 ns using the

Diff Delay

. The output frame pulses

(SONET/SDH, P0) can be independently offset with respect to each other using the

FP Delay

.

Figure 7 - Phase Delay Adjustments

DPLL1

DPLL2

P0 Fine Delay

p0_clk0

p0_clk1

p0_fp0

p0_fp1

P0

Synthesizer

Coarse Delay

Coarse Delay

FP Delay

FP Delay

fb_clk

p1_clk0

p1_clk1

P1 Fine Delay

Diff Delay

Diff Delay

diff0

diff1

SONET/SDH

APLL

sdh_clk0

sdh_clk1

sdh_fp0

sdh_fp1

SDH Fine Delay

Feedback

Synthesizer

DPLL1 Fine Delay

Coarse Delay

Coarse Delay

FP Delay

FP Delay

Coarse Delay

Coarse Delay

P1

Synthesizer

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL30122 | SONET/SDH Low Jitter Line Card Synchronizer |

| ZL30122GGG | SONET/SDH Low Jitter Line Card Synchronizer |

| ZL30406 | SONET/SDH Clock Multiplier PLL |

| ZL30406QGC | Digital Multimeter Clamp Battery Size Code:9V; Current Measuring Range:40.00/400.0A; Current Setting AC:400A; Current Setting DC:400A; Resistance Measuring Range:400 Ohm, 4000 - 40 - 400 kOhm; Voltage Measuring Range AC:600 V RoHS Compliant: NA |

| ZL30406QGC1 | SONET/SDH Clock Multiplier PLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL30121GGG2 | 制造商:Microsemi Corporation 功能描述:PB FREE LOW JITTER SYSTEM SYNCHRONIZER |

| ZL30121GGG2V2 | 制造商:Microsemi Corporation 功能描述:REV 2 PB FREE LOW JITTER SYSTEM SYNCHRO 制造商:Microsemi Corporation 功能描述:REV 2 PB FREE LOW JITTER SYSTEM SYNCHRO - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SONET/SDH SYNCH 100CABGA 制造商:Microsemi Corporation 功能描述:IC SONET/SDH SYNCH 100CABGA |

| ZL30121GGGV2 | 制造商:Microsemi Corporation 功能描述:LOW JITTER SYSTEM SYNCHRONIZER 制造商:Microsemi Corporation 功能描述:REV 2 LOW JITTER SYSTEM SYNCHRONIZER - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SONET/SDH SYNCH 100CABGA 制造商:Microsemi Corporation 功能描述:IC SONET/SDH SYNCH 100CABGA |

| ZL30122 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:SONET/SDH Low Jitter Line Card Synchronizer |

| ZL30122GGG | 制造商:Microsemi Corporation 功能描述:LOW JITTER SYSTEM SYNCHRONIZER 制造商:Microsemi Corporation 功能描述:SONET/SDH LOW JITTER LINE CARD SYNCHRONIZER 64CABGA - Trays 制造商:Microsemi Corporation 功能描述:IC SONET/SDH SYNCH 64CABGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。