- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373782 > ZL10311DTV-SOC (Zarlink Semiconductor Inc.) Digital Television DVB-T-On-a-Chip Processor PDF資料下載

參數(shù)資料

| 型號: | ZL10311DTV-SOC |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | Digital Television DVB-T-On-a-Chip Processor |

| 中文描述: | 數(shù)字電視的DVB - T -上一芯片處理器 |

| 文件頁數(shù): | 33/40頁 |

| 文件大小: | 670K |

| 代理商: | ZL10311DTV-SOC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當(dāng)前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

Data Sheet

ZL10310/ZL10311

33

Zarlink Semiconductor Inc.

6.12 Inter Integrated Circuit (I

2

C) Interface

The I

2

C interface provides a highly programmable interface to the industry-standard I

2

C (inter-integrated circuit)

serial bus. The I

2

C device contains a selection of functions that can be programmed to operate as a master, as a

slave, or as both a master and a slave on the I

2

C interface. I

2

C, unlike other designs, requires a minimum amount

of software to manage the I

2

C bus. In addition to sophisticated I

2

C bus protocol management, the I

2

C device

provides full data buffering, eliminating any time-dependent program interaction and further simplifying the task of

connecting to the I

2

C bus. The I

2

C interface complies with the Philips

Semiconductors I

2

C Specification, dated

1995.

Both the SCL and SDA pins require an external pull-up to 3.3V;

minimum resistor value of 1067 ohms.

6.13 Inter IC Sound (I

2

S) Audio Interface

The PCM Audio Output Controller provides an I

2

S Audio Interface. The audio outputs can be internally muted, and

a separate control output is not required. S/PDIF, surround, and center serial outputs can be obtained by using

Peripheral or General Purpose Port pins.

6.14 Clock and Reset Interface

The Clock and Reset interface provides inputs for the 2 primary clock signals, and also a System Reset input.

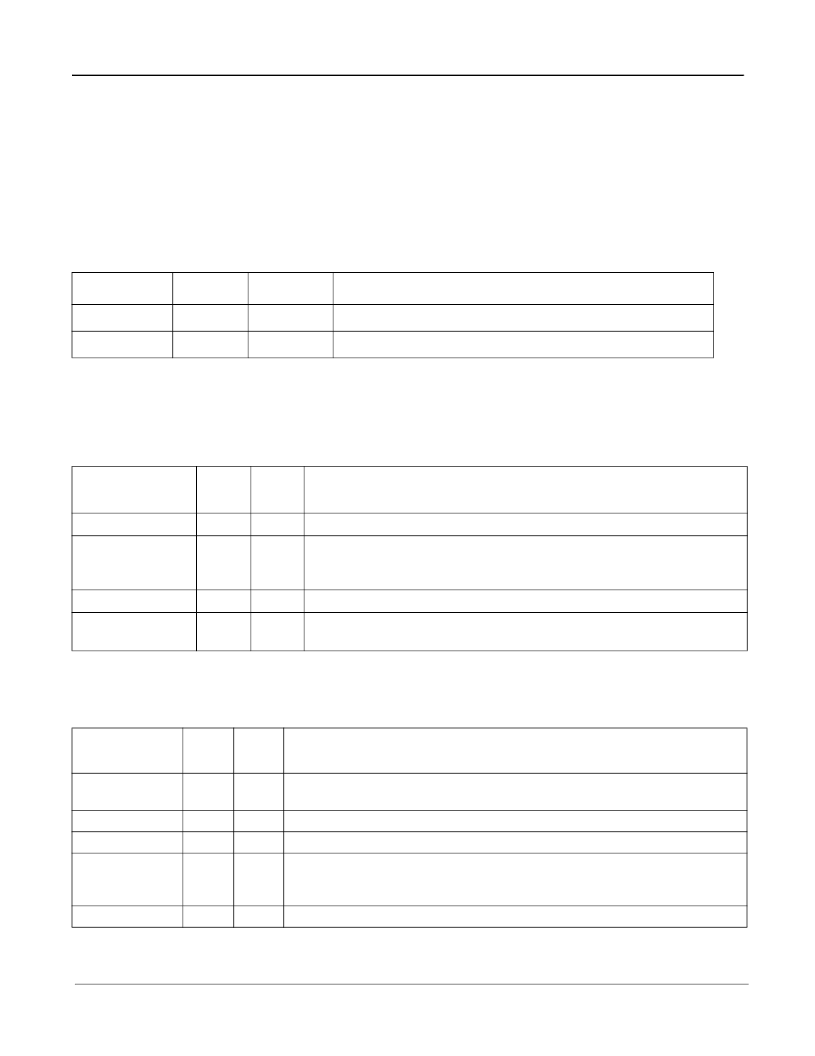

Pin Name

Pin No.

Pin Type

Description

I2C0_SCL

R25

O

I

2

C Bus Clock. Dedicated open drain clock.

I2C0_SDA

R26

O

I

2

C Bus Data. Dedicated open drain serial data/address.

Pin Name

Pin

No.

Pin

Type

Description

DA_BIT_CLK

C06

O

Digital Audio 64fs clock Output

DA_LR_CH_CLK

B04

O

Digital Audio Left-Right Channel Indicator Output.

A clock whose phase indicates the presence of left hand or right hand

data, and whose rate is equivalent to fs.

DA_OSAMP_CLK

A03

O

Digital Audio Oversampling Clock Output. 512/256 fs clock

DA_SER_DATA0

D06

O

Digital Audio Serial Data Output.

Main left and right serial audio data at a rate of 64fs

Pin Name

Pin

No.

Pin

Type

Description

OSC_PAD

C05

COFDM Crystal Oscillator - 20.48MHz Crystal Connection positive.

Also External 20.48MHz CXO Input

COFDM Crystal Oscillator - 20.48MHz Crystal Connection negative.

Main System Clock Input - 27MHz from External VCXO

Power-On Reset Input, from external POR generator. Active Low.

Must be held low for at least 100 microseconds after the 1.8V supply has

been established.

Connect to GND in normal operation. Defines production Test Mode B

OSC_PADN

CLK27_IN

NG_SYS_RST

B03

C18

A20

I

I

TMODE

B05

I

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL10312QCF | Satellite Demodulator |

| ZL10312QCG | Satellite Demodulator |

| ZL10312QCG1 | Satellite Demodulator |

| ZL10312UBH | Satellite Demodulator |

| ZL10312 | Satellite Demodulator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL10311GAC | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Digital Television DVB-T-On-a-Chip Processor |

| ZL10312 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Satellite Demodulator |

| ZL10312QCF | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Satellite Demodulator |

| ZL10312QCG | 制造商:Microsemi Corporation 功能描述: |

| ZL10312QCG1 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Satellite Demodulator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。