- 您現(xiàn)在的位置:買賣IC網 > PDF目錄11763 > XRT94L31IB (Exar Corporation)IC MAPPER DS3/E3/STS-1 504TBGA PDF資料下載

參數(shù)資料

| 型號: | XRT94L31IB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 133/133頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC MAPPER DS3/E3/STS-1 504TBGA |

| 標準包裝: | 24 |

| 應用: | 網絡切換 |

| 接口: | 總線 |

| 電源電壓: | 3.14 V ~ 3.47 V |

| 封裝/外殼: | 504-LBGA |

| 供應商設備封裝: | 504-TBGA(35x35) |

| 包裝: | 托盤 |

| 安裝類型: | 表面貼裝 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁當前第133頁

XRT94L31

99

REV. 1.0.1

3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER IC

NOTE: The values for t0 through t7 can be found in

NOTE: Test Conditions: TA = 25°C, VCC = 3.3V±5% and 2.5V±5%, unless otherwise specified.

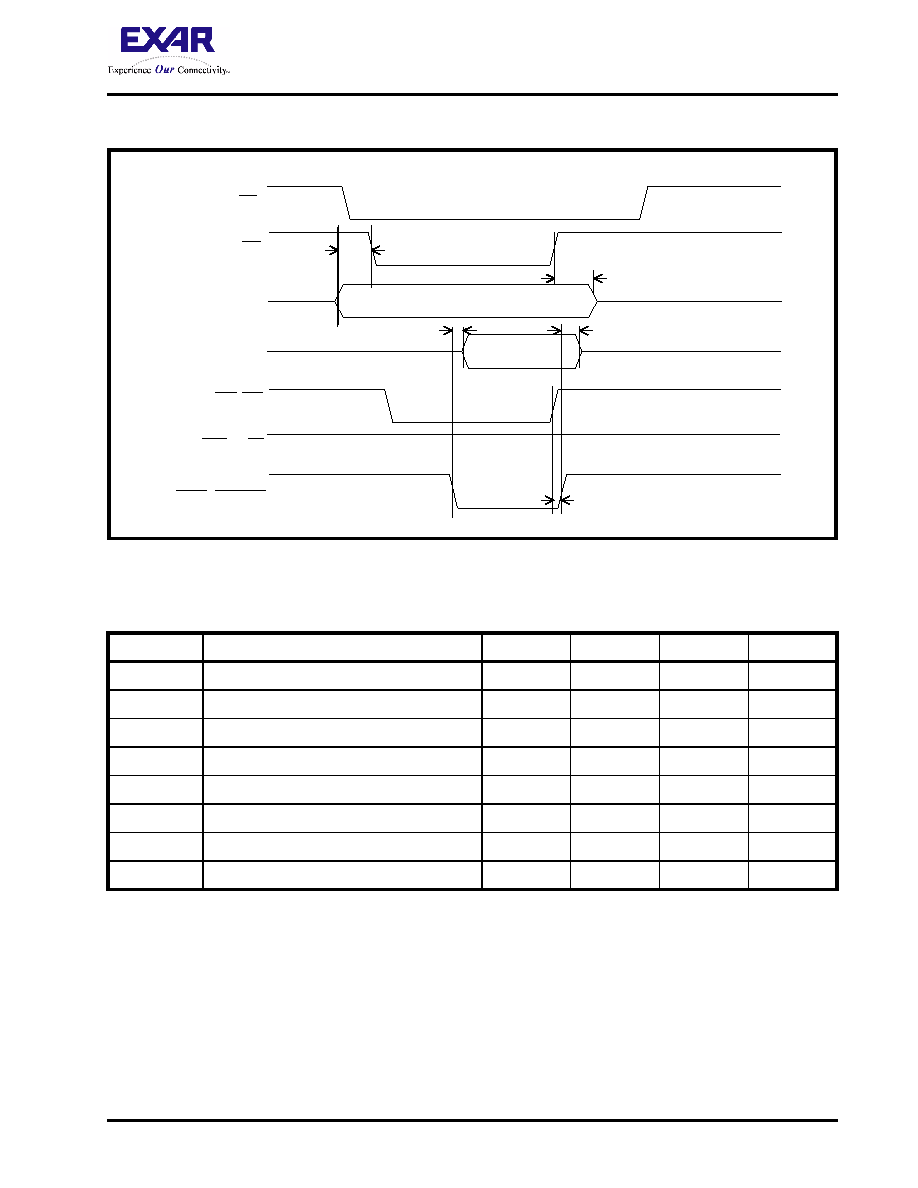

FIGURE 5. ASYNCHRONOUS MODE 2 - MOTOROLA (68K) PROGRAMMED I/O TIMING (READ CYCLE)

TABLE 4: TIMING INFORMATION FOR THE MICROPROCESSOR INTERFACE WHEN CONFIGURED TO OPERATE IN THE

MOTOROLA (68K) ASYNCHRONOUS MODE

TIMING

DESCRIPTION

MIN.

TYP.

MAX

UNITS

t0

Address setup time to pALE low

6

-

ns

t1

Address hold time to pALE high

6

-

ns

t2

Data setup time to pDS_L low

0

-

ns

t3

Data hold time to pDS_L low

160

-

ns

t4

pDS_L high to pRDY_L high (Write Cycle)

-

16

ns

t5

pRDY_L low to Data valid

-

15

ns

t6

pDS_L high to pRDY_L high (Read Cycle)

-

16

ns

t7

pRDY_L high to Data invalid

3

-

ns

Data

CS

ALE_AS

A[6:0]

D[7:0]

RD_DS

WR_R/W

RDY_DTACK

t

6

t

7

Address

t

0

t

1

t

5

相關PDF資料 |

PDF描述 |

|---|---|

| 413985-1 | CONN PLUG SMB RG-174 STR GOLD |

| VI-B4P-IW-F1 | CONVERTER MOD DC/DC 13.8V 100W |

| 413589-9 | CONN PLUG BNC RG-59 CRIMP GOLD |

| MS27473T20B1PB | CONN PLUG 79POS STRAIGHT W/PINS |

| 1408149-3 | CONN MMCX PLUG RT ANG RD-316 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XRT94L31IB-F | 功能描述:網絡控制器與處理器 IC Demapper RoHS:否 制造商:Micrel 產品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT94L31IB-L | 功能描述:網絡控制器與處理器 IC Mapper / Demapper RoHS:否 制造商:Micrel 產品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT94L33 | 制造商:EXAR 制造商全稱:EXAR 功能描述:-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER - SONET REGISTERS |

| XRT94L33_06 | 制造商:EXAR 制造商全稱:EXAR 功能描述:3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER IC DATA SHEET |

| XRT94L33_07 | 制造商:EXAR 制造商全稱:EXAR 功能描述:3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER - ATM REGISTERS |

發(fā)布緊急采購,3分鐘左右您將得到回復。