- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16428 > XR17V254IV-0A-EVB (Exar Corporation)EVAL BOARD FOR XR17V254 144LQFP PDF資料下載

參數(shù)資料

| 型號: | XR17V254IV-0A-EVB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 8/70頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR17V254 144LQFP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁

XR17V254

16

66MHZ PCI BUS QUAD UART WITH POWER MANAGEMENT SUPPORT

REV. 1.0.1

1.6.1

The Global Interrupt Register

The XR17V254 has a 32-bit wide register [INT0, INT1, INT2 and INT3] to provide interrupt information and

supports two interrupt schemes. The first scheme is an 8-bit indicator representing all 4 channels with each bit

representing each channel from 0 to 3. This permits the interrupt routine to quickly vector and serve that UART

channel and determine the source(s) in each individual routines. INT0 bit [0] represents the interrupt status for

UART channel 0 when its transmitter, receiver, line status, or modem port status requires service. Other bits in

the INT0 register provide indication for the other channels with bit [3] representing UART channel 3

respectively. Bits 4 to 7 are reserved and remains at logic zero.

The second scheme provides detail about the source of the interrupts for each UART channel. All the interrupts

are encoded into a 3-bit code. This 3-bit code represents 7 interrupts corresponding to individual UART’s

transmitter, receiver, line status, modem port status. INT1, INT2 and INT3 registers provide the 24-bit interrupt

status for all 4 channels. Bits [10:8] representing channel 0 and bits [19:17] representing channel 3

respectively. Bits [31:20] are reserved. All 4 channel interrupts status are available with a single DWORD read

operation. This feature allows the host quickly vectors and serves the interrupts, reducing service interval,

hence, reduce host bandwidth requirement.

All bits start up zero. A special interrupt condition is generated by the V254 upon awakening from sleep after all

four channels were put to sleep mode earlier. This wake-up interrupt is cleared by a read to the INT0 register.

shows the 4-byte interrupt register and its make up.

INT0 [7:0] Channel Interrupt Indicator

Each bit gives an indication of the channel that has requested for service. Bit [0] represents channel 0 and

bit [3] indicates channel 3. Logic one indicates the channel N [3:0] has called for service. The interrupt bit

clears after reading the appropriate register of the interrupting channel register, see Interrupt Clearing section.

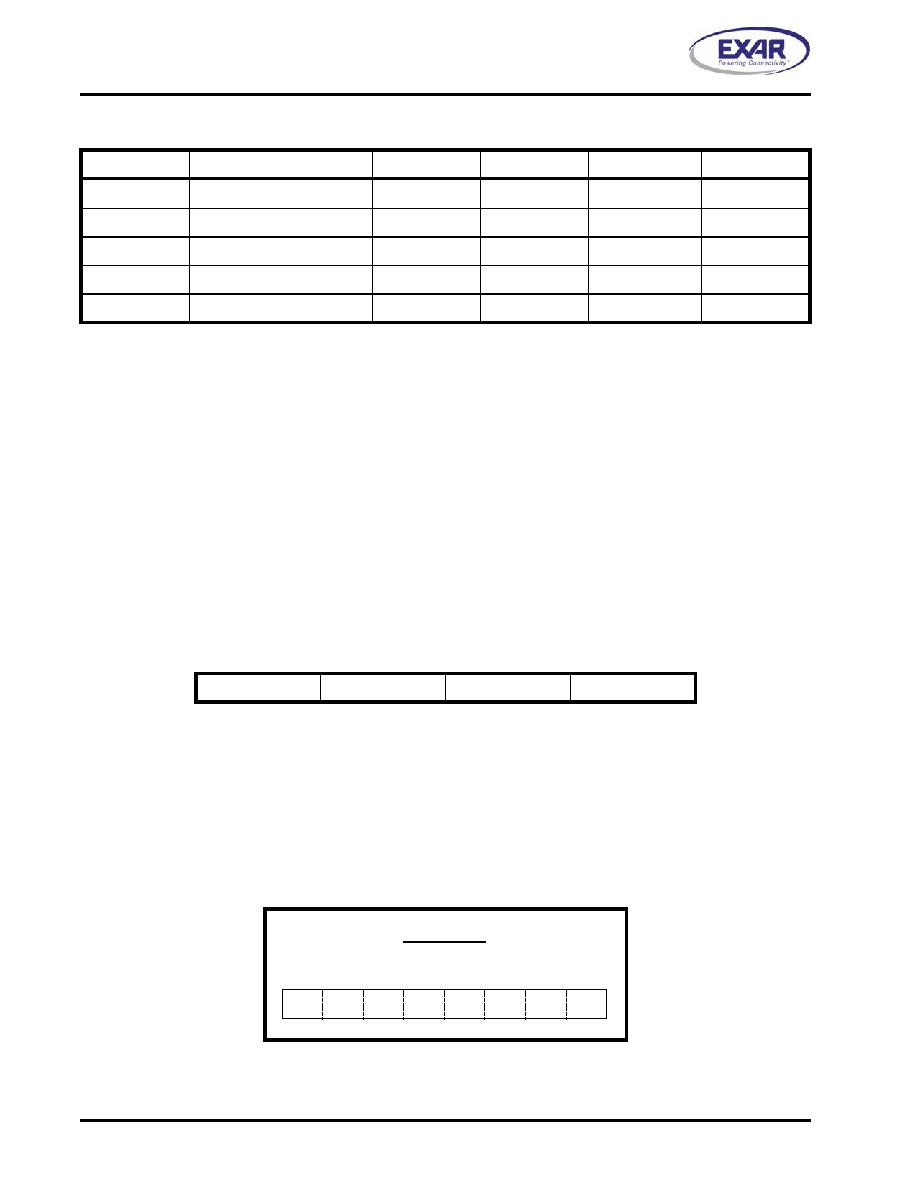

TABLE 7: DEVICE CONFIGURATION REGISTERS SHOWN IN DWORD ALIGNMENT

ADDRESS

REGISTER

BYTE 3 [31:24]

BYTE 2 [23:16]

BYTE 1 [15:8]

BYTE 0 [7:0]

0x080

-083

INTERRUPT (read-only)

INT3

INT2[

INT1

INT0

0x084-087

TIMER (read/write)

TIMERMSB

TIMERLSB

TIMER (reserved)

TIMERCNTL

0x088-08B

ANCILLARY1 (read/write)

SLEEP

RESET

REGA

8XMODE

0x08C-08F

ANCILLARY2 (read-only)

MPIOINT

REGB

DVID

DREV

0x090-093

MPIO (read/write)

MPIOSEL

MPIOINV

MPIO3T

MPIOLVL

GLOBAL INTERRUPT REGISTER (DWORD)

[default 0x00-00-00-00]

INT3 [31:24]

INT2 [23:16]

INT1 [15:8]

INT0 [7:0]

The INT0 register provides individual status for each channel

INT0 Register

Individual UART Channel Interrupt Status

Rsvd

Ch-3

Ch-2

Ch-1

Ch-0

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RPS0J102MCN1GS | CAP ALUM 1000UF 6.3V 20% SMD |

| EMM10DRMN | CONN EDGECARD 20POS .156 WW |

| GBA31DRMN-S288 | CONN EDGECARD 62POS .125 EXTEND |

| CM100505-18NGL | INDUCTOR CHIP 18NH 1005 SMD |

| 1-6828247-5 | CA,SM,MTRJ-SC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR17V254IV-F | 功能描述:UART 接口集成電路 66MHz Quad PCI UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17V258 | 制造商:EXAR 制造商全稱:EXAR 功能描述:66MHZ PCI BUS OCTAL UART WITH POWER MANAGEMENT SUPPORT |

| XR17V258_08 | 制造商:EXAR 制造商全稱:EXAR 功能描述:66MHZ PCI BUS OCTAL UART WITH POWER MANAGEMENT SUPPORT |

| XR17V258IV | 功能描述:UART 接口集成電路 66MHz Octal PCI UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17V258IV-0A-EVB | 功能描述:UART 接口集成電路 Supports V258 144 ld TQFP, PCI Interface RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。