- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16428 > XR17V254IV-0A-EVB (Exar Corporation)EVAL BOARD FOR XR17V254 144LQFP PDF資料下載

參數(shù)資料

| 型號: | XR17V254IV-0A-EVB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 70/70頁 |

| 文件大?。?/td> | 0K |

| 描述: | EVAL BOARD FOR XR17V254 144LQFP |

| 標準包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁當前第70頁

XR17V254

9

REV. 1.0.1

66MHZ PCI BUS QUAD UART WITH POWER MANAGEMENT SUPPORT

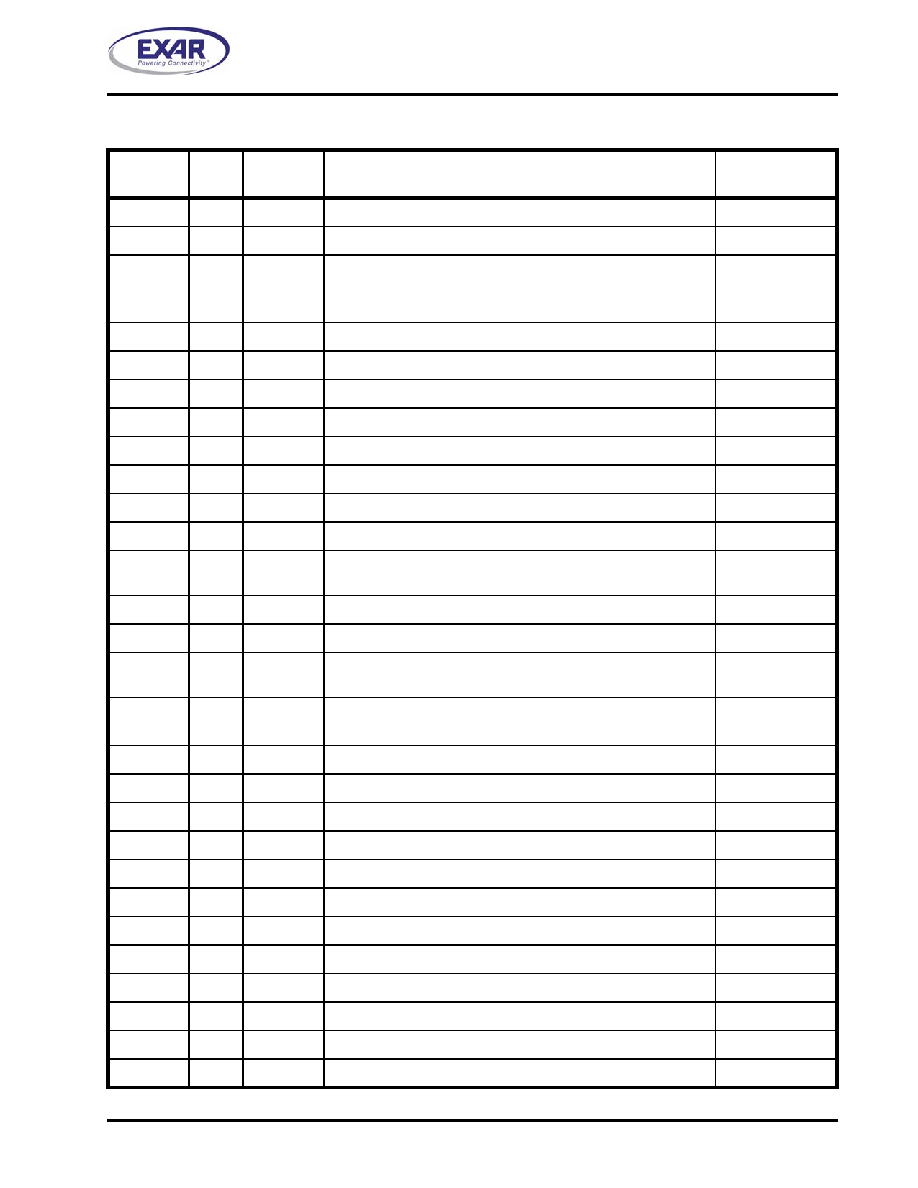

TABLE 1: PCI LOCAL BUS CONFIGURATION SPACE REGISTERS

ADDRESS

OFFSET

BITS

TYPE

DESCRIPTION

RESET VALUE

(HEX OR BINARY)

0x00

31:16

EWR

Device ID (Exar device ID number)

0x0254

15:0

EWR

Vendor ID (Exar) specified by PCISIG

0x13A8

0x04

31

30

29:28

RWC

RO

Parity error detected. Cleared by writing a logic 1.

System error detected. Cleared by writing a logic 1.

Unused

0b

00b

27

RO

Target Abort.

0b

26:25

RO

DEVSEL# timing.

00b

24

RO

Unemployments bus master error reporting bit

0b

23

RO

Fast back to back transactions are supported

1b

22

RO

Reserved Status bit

0b

21

RO

66MHz capable

20

RO

Capabilities List

1b

19:16

RO

Reserved Status bits

0000b

15:9,7,

5,4,3,2

RO

Command bits (reserved)

0x0000

8

RWR

SERR# driver enable. logic 1=enable driver and 0=disable driver

0b

6

RWR

Parity error enable. logic 1=respond to parity error and 0=ignore

0b

1

RWR

Command controls a device’s response to mem space accesses:

0=disable mem space accesses, 1=enable mem space accesses

0b

0

RO

Device’s response to I/O space accesses is disabled.

(0 = disable I/O space accesses)

0b

0x08

31:8

EWR

Class Code (Default is ’Simple 550 Communication Controller’)

0x070002

7:0

RO

Revision ID (Exar device revision number)

Current Rev. value

0x0C

31:24

RO

BIST (Built-in Self Test)

0x00

23:16

RO

Header Type (a single function device with one BAR)

0x00

15:8

RO

Unimplemented Latency Timer (needed only for bus master)

0x00

7:0

RO

Unimplemented Cache Line Size

0x00

0x10

31:11

RWR

Memory Base Address Register (BAR)

0x00

10:0

RO

Claims a 2K address space for the memory mapped UARTs

0x000

0x14

31:0

RO

Unimplemented Base Address Register (returns zeros)

0x00000000

0x18h

31:0

RO

Unimplemented Base Address Register (returns zeros)

0x00000000

0x1C

31:0

RO

Unimplemented Base Address Register (returns zeros)

0x00000000

0x20

31:0

RO

Unimplemented Base Address Register (returns zeros)

0x00000000

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RPS0J102MCN1GS | CAP ALUM 1000UF 6.3V 20% SMD |

| EMM10DRMN | CONN EDGECARD 20POS .156 WW |

| GBA31DRMN-S288 | CONN EDGECARD 62POS .125 EXTEND |

| CM100505-18NGL | INDUCTOR CHIP 18NH 1005 SMD |

| 1-6828247-5 | CA,SM,MTRJ-SC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR17V254IV-F | 功能描述:UART 接口集成電路 66MHz Quad PCI UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17V258 | 制造商:EXAR 制造商全稱:EXAR 功能描述:66MHZ PCI BUS OCTAL UART WITH POWER MANAGEMENT SUPPORT |

| XR17V258_08 | 制造商:EXAR 制造商全稱:EXAR 功能描述:66MHZ PCI BUS OCTAL UART WITH POWER MANAGEMENT SUPPORT |

| XR17V258IV | 功能描述:UART 接口集成電路 66MHz Octal PCI UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17V258IV-0A-EVB | 功能描述:UART 接口集成電路 Supports V258 144 ld TQFP, PCI Interface RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。