- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4214 > XCV405E-8FG676C (Xilinx Inc)IC FPGA 1.8V C-TEMP 676-FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XCV405E-8FG676C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 46/118頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1.8V C-TEMP 676-FBGA |

| 產(chǎn)品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | Virtex®-E EM |

| LAB/CLB數(shù): | 2400 |

| 邏輯元件/單元數(shù): | 10800 |

| RAM 位總計(jì): | 573440 |

| 輸入/輸出數(shù): | 404 |

| 門數(shù): | 129600 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 676-BGA |

| 供應(yīng)商設(shè)備封裝: | 676-FBGA(27x27) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁當(dāng)前第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁

Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays

DS025-2 (v3.0) March 21, 2014

Module 2 of 4

29

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

Initialization

The block SelectRAM+ memory can initialize during the

device configuration sequence. The 16 initialization properties

of 64 hex values each (a total of 4096 bits) set the initialization

of each RAM. These properties appear in Table 17. Any initial-

ization properties not explicitly set configure as zeros. Partial

initialization strings pad with zeros. Initialization strings

greater than 64 hex values generate an error. The RAMs can

be simulated with the initialization values using generics in

VHDL simulators and parameters in Verilog simulators.

Initialization in VHDL and Synopsys

The block SelectRAM+ structures can be initialized in VHDL

for both simulation and synthesis for inclusion in the EDIF

output file. The simulation of the VHDL code uses a generic

to pass the initialization. Synopsys FPGA compiler does not

presently support generics. The initialization values instead

attach as attributes to the RAM by a built-in Synopsys

dc_script. The translate_off statement stops synthesis

translation of the generic statements. The following code

illustrates a module that employs these techniques.

Initialization in Verilog and Synopsys

The block SelectRAM+ structures can be initialized in Verilog

for both simulation and synthesis for inclusion in the EDIF

output file. The simulation of the Verilog code uses a def-

param to pass the initialization. The Synopsys FPGA com-

piler does not presently support defparam. The initialization

values instead attach as attributes to the RAM by a built-in

Synopsys dc_script. The translate_off statement stops syn-

thesis translation of the defparam statements. The following

code illustrates a module that employs these techniques.

Design Examples

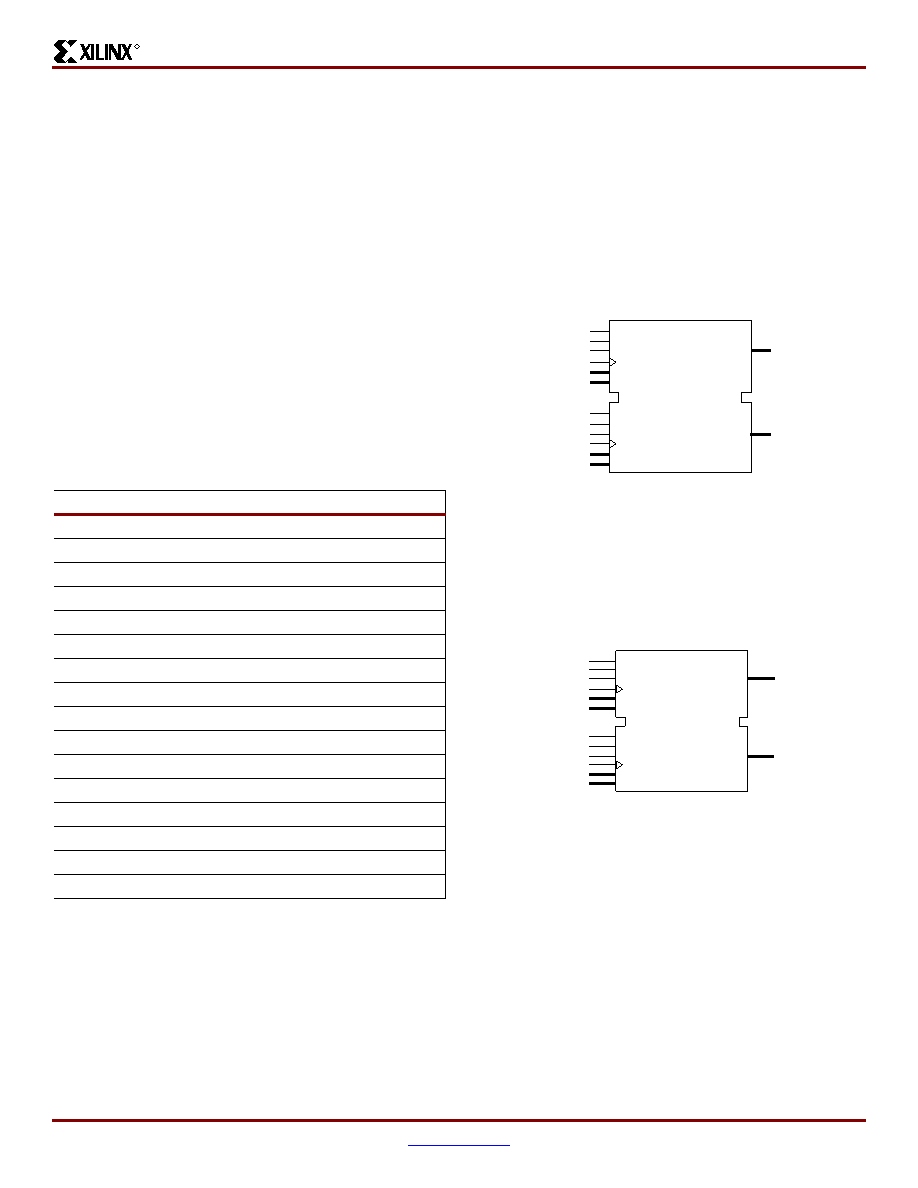

Creating a 32-bit Single-Port RAM

The true dual-read/write port functionality of the block

SelectRAM+ memory allows a single port, 128 deep by

32-bit wide RAM to be created using a single block

SelectRAM+ cell as shown inTable 35.

Interleaving the memory space, setting the LSB of the

address bus of Port A to 1 (VCC), and the LSB of the

address bus of Port B to 0 (GND), allows a 32-bit wide sin-

gle port RAM to be created.

Creating Two Single-Port RAMs

The true dual-read/write port functionality of the block

SelectRAM+ memory allows a single RAM to be split into two

single port memories of 2K bits each as shown in Figure 36.

In this example, a 512K x 4 RAM (Port A) and a 128 x 16

RAM (Port B) are created out of a single block SelectRAM+.

The address space for the RAM is split by fixing the MSB of

Port A to 1 (VCC) for the upper 2K bits and the MSB of Port

B to 0 (GND) for the lower 2K bits.

Block Memory Generation

The CoreGen program generates memory structures using

the block SelectRAM+ features. This program outputs

VHDL or Verilog simulation code templates and an EDIF file

for inclusion in a design.

Table 17:

RAM Initialization Properties

Property

Memory Cells

INIT_00

255 to 0

INIT_01

511 to 256

INIT_02

767 to 512

INIT_03

1023 to 768

INIT_04

1279 to 1024

INIT_05

1535 to 1280

INIT_06

1791 to 2047

INIT_07

2047 to 1792

INIT_08

2303 to 2048

INIT_09

2559 to 2304

INIT_0a

2815 to 2560

INIT_0b

3071 to 2816

INIT_0c

3327 to 3072

INIT_0d

3583 to 3328

INIT_0e

3839 to 3584

INIT_0f

4095 to 3840

Figure 35: Single Port 128 x 32 RAM

Figure 36: 512 x 4 RAM and 128 x 16 RAM

WEB

ENB

RSTB

CLKB

ADDRB[7:0]

DIB[15:0]

WEA

ENA

RSTA

CLKA

ADDRA[7:0]

DIA[15:0]

ADDR[6:0], V

CC

CLK

EN

RST

CLK

EN

RST

WE

DI[31:16]

ADDR[6:0], GND

DI[15:0]

DOA[15:0]

DO[31:16]

DO[15:0]

DOB[15:0]

RAMB4_S16_S16

ds022_036_121399

WEB

ENB

RSTB

CLKB

ADDRB[7:0]

DIB[15:0]

WEA

ENA

RSTA

CLKA

ADDRA[9:0]

DIA[3:0]

V

CC, ADDR1[8:0]

DI1[3:0]

WE1

EN1

RST1

CLK1

WE2

EN2

RST2

CLK2

GND, ADDR2[6:0]

DI2[15:0]

DOA[3:0]

DO1[3:0]

DO2[15:0]

DOB[15:0]

RAMB4_S4_S16

ds022_037_121399

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCV405E-7FG676I | IC FPGA 1.8V 676-BGA |

| XC6VLX195T-1FFG784C | IC FPGA VIRTEX 6 199K 784FFGBGA |

| XC6VCX130T-2FFG784I | IC FPGA VIRTEX 6 128K 784FFGBGA |

| XC4VLX60-11FF668I | IC FPGA VIRTEX-4LX 668FFBGA |

| XC4VLX60-12FFG668C | IC FPGA VIRTEX-4 LX 60K 668FCBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCV405E-8FG676I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-8FG900C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-8FG900I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV50 | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XCV50-4BG256C | 功能描述:IC FPGA 2.5V C-TEMP 256-PBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Virtex® 標(biāo)準(zhǔn)包裝:1 系列:Kintex-7 LAB/CLB數(shù):25475 邏輯元件/單元數(shù):326080 RAM 位總計(jì):16404480 輸入/輸出數(shù):350 門數(shù):- 電源電壓:0.97 V ~ 1.03 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:900-BBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:900-FCBGA(31x31) 其它名稱:122-1789 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。