- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371305 > XA-H3 (NXP Semiconductors N.V.) CMOS 16-bit highly integrated microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | XA-H3 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | CMOS 16-bit highly integrated microcontroller |

| 中文描述: | 的CMOS 16位高度集成的微控制器 |

| 文件頁(yè)數(shù): | 15/36頁(yè) |

| 文件大小: | 183K |

| 代理商: | XA-H3 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

Philips Semiconductors

Preliminary specification

XA-H3

CMOS 16-bit highly integrated microcontroller

1999 Sep 24

15

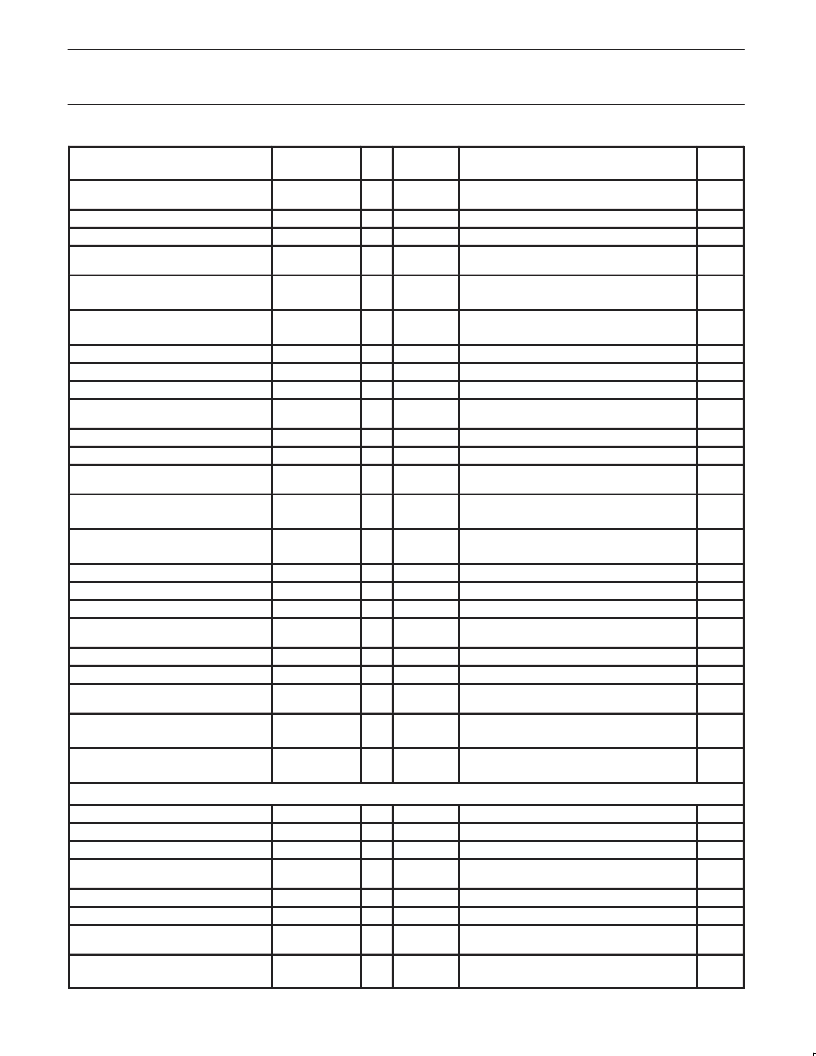

MMR Name

Reset

Value

Description

Address

Offset

Size

Read/Write or

Read Only

Buffer Base Register Ch. 1 Rx

R/W

8

114h

Wrap Reload Value for A15 – A8, A7 – A0

reloaded to zero by hardware

Upper Bound (plus 1) on A15 – A0

00h

Buffer Bound Register Ch.1 Rx

R/W

16

116h

0000h

Address Pointer Reg Ch.1 Rx

R/W

16

118h

Current Address pointer A15 – A0

0000h

Byte Count Register Ch.1 Rx

R/W

16

11Ah

Corresponds to A15 – A0 Byte Count, generates

interrupt if enabled and byte count exceeded.

11Ch = Byte 0 = older,

11Dh = Byte 1 = younger

11Eh = Byte 2 = older,

11Fh = Byte 3 = younger

Control Register

0000h

Data FIFO Register Ch.1 Lo Rx

R/W

16

11Ch

00h

00h

00h

00h

00h

Data FIFO Register Ch.1 Hi Rx

R/W

16

11Eh

DMA Control Register Ch.2 Rx

R/W

8

120h

FIFO Control & Status Register Ch.2 Rx

R/W

8

121h

Control & Status Register

00h

Segment Register Ch. 2 Rx

R/W

8

122h

Points to 64 k data segment

00h

Buffer Base Register Ch. 2 Rx

R/W

8

124h

Wrap Reload Value for A15 – A8, A7 – A0

reloaded to zero by hardware

Upper Bound (plus 1) on A15 – A0

00h

Buffer Bound Register Ch.2 Rx

R/W

16

126h

0000h

Address Pointer Reg Ch.2 Rx

R/W

16

128h

Current Address pointer A15 – A0

0000h

Byte Count Register Ch.2 Rx

R/W

16

12Ah

Corresponds to A15 – A0 Byte Count, generates

interrupt if enabled and byte count exceeded.

12Ch = Byte 0 = older,

12Dh = Byte 1 = younger

12Eh = Byte 2 = older,

12Fh = Byte 3 = younger

Control Register

0000h

Data FIFO Register Ch.2 Lo Rx

R/W

16

12Ch

00h

00h

00h

00h

00h

Data FIFO Register Ch.2 Hi Rx

R/W

16

12Eh

DMA Control Register Ch.3 Rx

R/W

8

130h

FIFO Control & Status Register Ch.3 Rx

R/W

8

131h

Control & Status Register

00h

Segment Register Ch. 3 Rx

R/W

8

132h

Points to 64 k data segment

00h

Buffer Base Register Ch. 3 Rx

R/W

8

134h

Wrap Reload Value for A15 – A8, A7 – A0

reloaded to zero by hardware

Upper Bound (plus 1) on A15 – A0

00h

Buffer Bound Register Ch.3 Rx

R/W

16

136h

0000h

Address Pointer Reg Ch.3 Rx

R/W

16

138h

Current Address pointer A15 – A0

0000h

Byte Count Register Ch.3 Rx

R/W

16

13Ah

Corresponds to A15 – A0 Byte Count, generates

interrupt if enabled and byte count exceeded.

13Ch = Byte 0 = older,

13Dh = Byte 1 = younger

13Eh = Byte 2 = older,

13Fh = Byte 3 = younger

0000h

Data FIFO Register Ch.3 Lo Rx

R/W

16

13Ch

00h

00h

00h

00h

Data FIFO Register Ch.3 Hi Rx

R/W

16

13Eh

Tx DMA Registers

DMA Control Register Ch.0 Tx

R/W

8

140h

Control Register

00h

FIFO Control & Status Register Ch.0 Tx

R/W

8

141h

Control & Status Register

00h

Segment Register Ch. 0 Tx

R/W

8

142h

Points to 64 k data segment

00h

Buffer Base Register Ch. 0 Tx

R/W

8

144h

Wrap Reload Value for A15 – A8, A7 – A0

reloaded to zero by hardware

Upper Bound (plus 1) on A15 – A0

00h

Buffer Bound Register Ch.0 Tx

R/W

16

146h

0000h

Address Pointer Reg Ch.0 Tx

R/W

16

148h

Current Address pointer A15 – A0

0000h

Byte Count Register Ch.0 Tx

R/W

16

14Ah

Corresponds to A15 – A0 Byte Count, generates

interrupt if enabled and byte count exceeded.

14C = Byte0 = older

14D = Byte 1 = younger

0000h

Data FIFO Register Ch.0 Tx

R/W

16

14Ch

0000h

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XA-H4 | Single-chip 16-bit microcontroller |

| XACA04SPEC0304 | CONTROL STATION 4WAY |

| XACA06SPEC0305 | CONTROL STATION 6WAY |

| XACA215 | FERNSTEUEREINHEIT |

| XALB222 | WIPPSCHALTER ZB2 STEUERGEHAEUSE TASTEN 2 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XA-H4 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Single-chip 16-bit microcontroller |

| XAI.50V2200 | 制造商:Xicon Passive Components 功能描述: |

| XAIR1-3402-101B | 制造商:Advantech Co Ltd 功能描述:CARRIER BOARD, AIR PRODUCTS 3402-101B3 - Bulk |

| XAIR1-3402-CARTON | 制造商:Advantech Co Ltd 功能描述:D-AIR01-SOM7562-01 - OUTER CARTON - Bulk |

| XAITD-100 | 制造商:RHOMBUS-IND 制造商全稱:Rhombus Industries Inc. 功能描述:XAITD Series FAST / TTL Buffered 10-Tap Delay Modules |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。