- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378744 > UPD70741 (NEC Corp.) V821TM 32-/16-BIT MICROPROCESSOR PDF資料下載

參數(shù)資料

| 型號: | UPD70741 |

| 廠商: | NEC Corp. |

| 元件分類: | 16位微控制器 |

| 英文描述: | V821TM 32-/16-BIT MICROPROCESSOR |

| 中文描述: | V821TM 32-/16-BIT微處理器 |

| 文件頁數(shù): | 60/112頁 |

| 文件大小: | 605K |

| 代理商: | UPD70741 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁當(dāng)前第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁

μ

PD70741

60

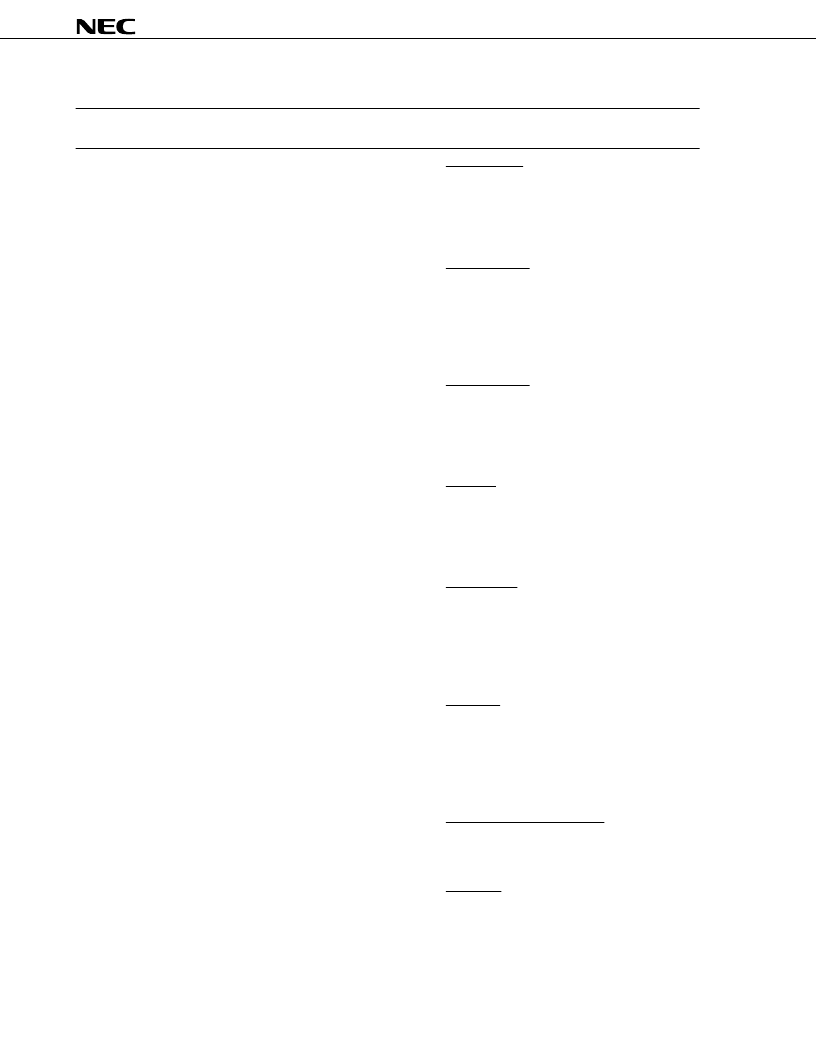

Table 15-1. Instruction Mnemonics (In Alphabetical Order) (8/9)

Instruction

Operand (s)

Format

CY OV

S

Z

Instruction function

mnemonic

SHL

imm5, reg2

II

*

0

*

*

Logical left shift:

Zero-extends the 5-bit immediate data to 32 bits, shifts

every bit of the word data in the reg2-specified register

to the left by the number of times specified by the

extended immediate data, then stores the result into

the reg2-specified register.

SHR

reg1, reg2

I

*

0

*

*

Logical right shift:

Shifts every bit of the word data in the reg2-specified

register to the right by the number of times specified

with the reg1-specified register’s lowest 5 bits, then

stores the result into the reg2-specified register. In

logical right shift operations, the MSB is loaded with

0 at each shift.

SHR

imm5, reg2

II

*

0

*

*

Logical right shift:

Zero-extends the 5-bit immediate data to 32 bits, shifts

every bit of the word data in the reg2-specified register

to the right by the number of times specified by the

extended immediate data, then stores the result into

the reg2-specified register.

ST.B

reg2, disp16 [reg1]

VI

-

-

-

-

Byte store:

Sign-extends the 16-bit displacement to 32 bits and

adds the 32-bit displacement and the content of the

reg1-specified register to generate a 32-bit unsigned

address, then transfers the reg2-specified register’s

lowest 8 bits to the generated address.

ST.H

reg2, disp16 [reg1]

VI

-

-

-

-

Halfword store:

Sign-extends the 16-bit displacement to 32 bits with

its bit 0 masked to 0, and adds the content of the reg1-

specified register and the 32-bit displacement to generate

a 32-bit unsigned address, then transfers the reg2-

specified register’s lower 16 bits to the generated

address.

ST.W

reg2, disp16 [reg1]

VI

-

-

-

-

Word store:

Sign-extends the 16-bit displacement to 32 bits with

its bits 0 and 1 masked to 0, and adds the reg1-

specified register and the 32-bit displacement to generate

a 32-bit unsigned address, then transfers the word

data of the reg2-specified register to the generated

address.

STSR

regID, reg2

II

-

-

-

-

Storing system register contents:

Loads the reg2-specified register with the content of

the system register specified by the system register

number (regID).

SUB

reg1, reg2

I

*

*

*

*

Subtraction:

Subtracts the word data in the reg1-specified register

from that in the reg2-specified register, then stores the

result into the reg2-specified register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD70741GC-25-8EU | V821TM 32-/16-BIT MICROPROCESSOR |

| UPD70F3003A | V853TM 32-/16-BIT SINGLE-CHIP MICROCONTROLLER |

| UPD70F3003AGC-25-8EU | Circular Connector; No. of Contacts:24; Series:MS27467; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:25; Circular Contact Gender:Pin; Circular Shell Style:Straight Plug; Insert Arrangement:25-24 RoHS Compliant: No |

| UPD70F3025AGC-25-8EU | V853TM 32-/16-BIT SINGLE-CHIP MICROCONTROLLER |

| UPD70F3003AGC-33-8EU | LJT 29C 29#16 PIN PLUG |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD70741GC-25-8EU | 制造商:NEC 制造商全稱:NEC 功能描述:V821TM 32-/16-BIT MICROPROCESSOR |

| UPD70742GD-25-LML | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| UPD70F30025AGC-25 | 制造商:NEC 制造商全稱:NEC 功能描述:32-bit RISC Microcontrollers |

| UPD70F30025AGC-33 | 制造商:NEC 制造商全稱:NEC 功能描述:32-bit RISC Microcontrollers |

| UPD70F3003A | 制造商:NEC 制造商全稱:NEC 功能描述:V853TM 32-/16-BIT SINGLE-CHIP MICROCONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。