- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385920 > TDC2302B (Texas Instruments, Inc.) STS-3/STM-1 Line Interface(STS-3/STM-1線性接口) PDF資料下載

參數(shù)資料

| 型號: | TDC2302B |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | STS-3/STM-1 Line Interface(STS-3/STM-1線性接口) |

| 中文描述: | STS-3/STM-1線路接口(STS-3/STM-1線性接口) |

| 文件頁數(shù): | 15/17頁 |

| 文件大?。?/td> | 390K |

| 代理商: | TDC2302B |

TDC2302B

STS-3/STM-1 LINE INTERFACE

SDNS002 – SEPTEMBER 1992 – REVISED JUNE 1993

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

15

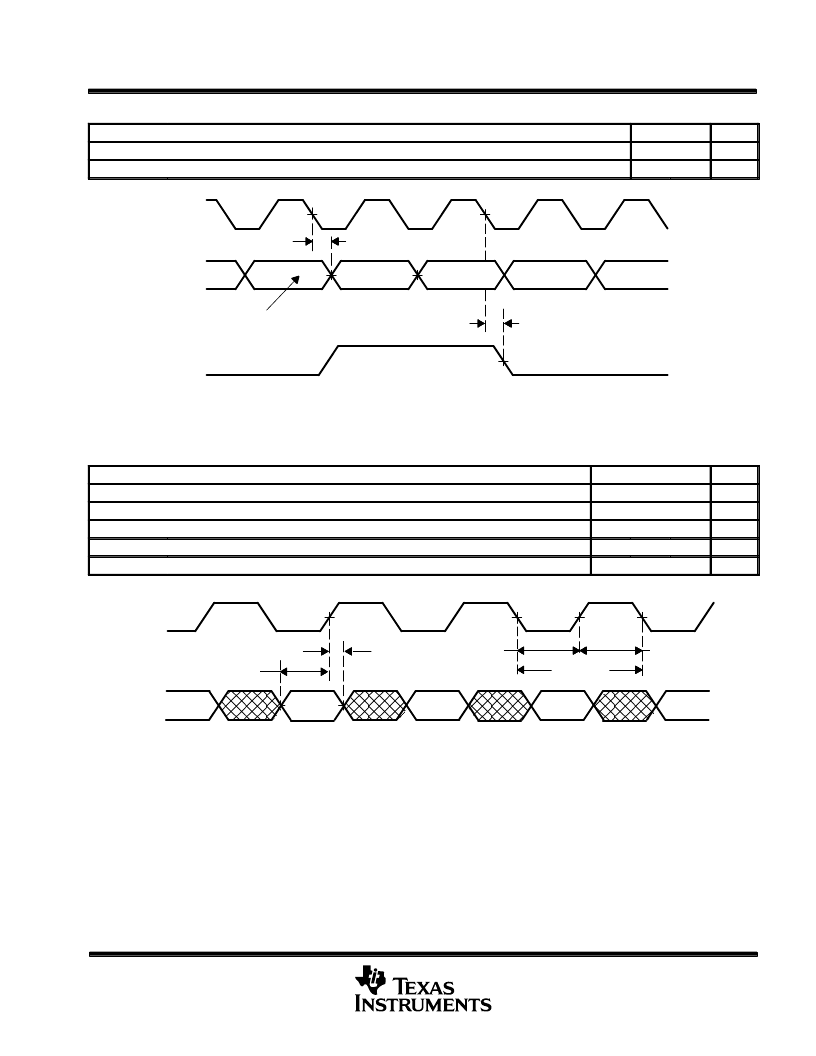

timing requirements (see Figures 16 and 17) (continued)

MIN

MAX

UNIT

td(RXBD)

td(B1E)

Delay time, RXBD after RXBC

↓

Delay time, B1ERR

↓

after RXBC

↓

0

6

ns

0

6

ns

td(B1E)

td(RXBD)

B1ERR

RXBDn

RXBC

Last Data Byte/Nibble

of the First Row of the

Payload

Bit Error

B1 Parity Bit 7

Bit O.K.

B1 Parity Bit 6

B1

MSB Nibble

B1

LSB Nibble

NOTE: Four time slots of B1ERR output are shown; up to eight bits may be in error in a given frame.

Figure 16. B1 Error Pulse Timing – Nibble Mode

MIN

NOM

MAX

UNIT

tw(TXSC)L

tw(TXSC)H

tc(TXSC)

tsu(TXSD)

th(TXSD)

Pulse duration, TXSC low

2.9

ns

Pulse duration, TXSC high

2.9

ns

Clock cycle time, TXSC

Setup time, TXSD before TXSC

↑

Hold time, TXSD after TXSC

↑

6.43

ns

1

ns

1.25

ns

TXSD

TXSC

tsu (TXBD)

th(TXBD)

tw(TXSC)H

tc(TXSC)

tw(TXSC)L

ìììì

ìììì

ìììì

ìììì

ìììì

ìììì

Figure 17. Line-Side PECL Output Timing

ìììì

ìììì

ìììì

ììììì

ììììì

ììììì

相關PDF資料 |

PDF描述 |

|---|---|

| TEA1721AT | Ultra-low standby SMPS controller with integrated power switch |

| TEC3016 | High-Speed RISC Delay Modules |

| TEC3020 | High-Speed RISC Delay Modules |

| TFB2022AM | Futurebus+ Data Path Unit(面向未來總線數(shù)據(jù)線單元) |

| TFS183B | Development specification |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TDC-24-AKA-030 | 制造商:ATC DIVERSIFIED ELECTRONICS 功能描述:TIME DELAY RELAY DELAY ON OPERATE (RELAY OUTPUT) |

| TDC-24-AKA-060 | 制造商:ATC 功能描述: 制造商:American Technical Ceramics Corp 功能描述: |

| TDC274035NSE-F | 制造商:CDE 制造商全稱:Cornell Dubilier Electronics 功能描述:Dipped, Radial Leaded, Solid Tantalum Capacitors |

| TDC274050NSE-F | 制造商:CDE 制造商全稱:Cornell Dubilier Electronics 功能描述:Dipped, Radial Leaded, Solid Tantalum Capacitors |

| TDC274K035NLE | 制造商:Mallory Sonalert Products Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。