- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385920 > TDC2302B (Texas Instruments, Inc.) STS-3/STM-1 Line Interface(STS-3/STM-1線性接口) PDF資料下載

參數(shù)資料

| 型號(hào): | TDC2302B |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | STS-3/STM-1 Line Interface(STS-3/STM-1線性接口) |

| 中文描述: | STS-3/STM-1線路接口(STS-3/STM-1線性接口) |

| 文件頁(yè)數(shù): | 13/17頁(yè) |

| 文件大小: | 390K |

| 代理商: | TDC2302B |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)

TDC2302B

STS-3/STM-1 LINE INTERFACE

SDNS002 – SEPTEMBER 1992 – REVISED JUNE 1993

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

13

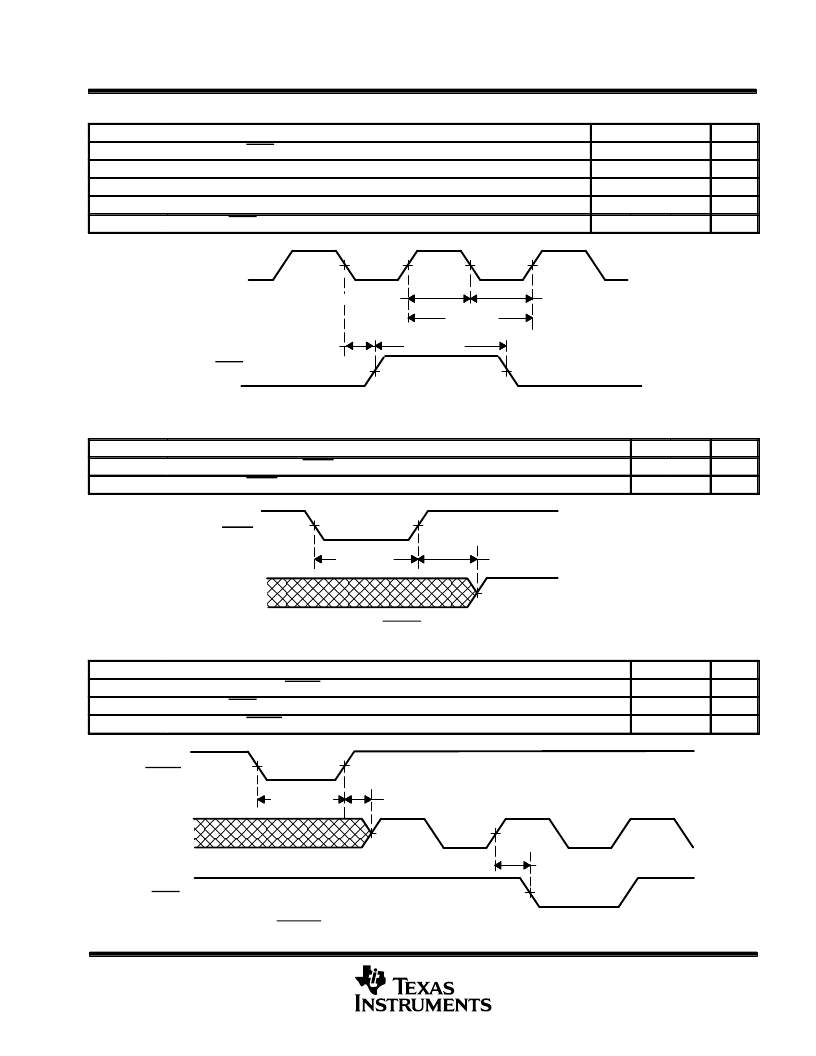

timing requirements (see Figures 11, 12, and 13) (continued)

MIN

NOM

MAX

UNIT

tw(TXRF)2

tw(TXRC)H

tw(TXRC)L

tc(TXRC)

td(TXRF)

Pulse duration, TXRF

25.72

ns

Pulse duration, TXRC high

9

ns

Pulse duration, TXRC low

9

ns

Clock cycle time, TXRC

Delay time, TXRF

↑

after TXRC

↓

25.72

ns

0

6

ns

TXRC

tw(TXRC)H

tw(TXRC)L

tc(TXRC)

td(TXRF)

TXRF

tw(TXRF)2

Figure 11. Terminal-Side Nibble Reference Signals Output (TPINV high)

MIN

MAX

UNIT

td(OOF/LOF)

tw(OOFN)

Delay time, OOF/LOF after OOFN

↑

Pulse duration, OOFN

0

312

ns

105

ns

OOF/LOF

ììììììììììì

ììììììììììì

Figure 12. OOFN Resetting Frame

td(OOF/LOF)

tw(OOFN)

OOFN

Active High Only

MIN

MAX

UNIT

td(TXRC)R

td(TXRF)

tw(RESET)

Delay time, TXRC after RESET

↑

Delay time, TXRF

↓

after TXRC

↑

Pulse duration, RESET low

6

30

ns

0

6

ns

105

ns

TXRC

ìììììììììì

ìììììììììì

ìììììììììì

td(TXRC)R

RESET

td(TXRF)

TXRF

Figure 13. RESET Effect of Reference Clock and Frame (TPINV low)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TEA1721AT | Ultra-low standby SMPS controller with integrated power switch |

| TEC3016 | High-Speed RISC Delay Modules |

| TEC3020 | High-Speed RISC Delay Modules |

| TFB2022AM | Futurebus+ Data Path Unit(面向未來(lái)總線數(shù)據(jù)線單元) |

| TFS183B | Development specification |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TDC-24-AKA-030 | 制造商:ATC DIVERSIFIED ELECTRONICS 功能描述:TIME DELAY RELAY DELAY ON OPERATE (RELAY OUTPUT) |

| TDC-24-AKA-060 | 制造商:ATC 功能描述: 制造商:American Technical Ceramics Corp 功能描述: |

| TDC274035NSE-F | 制造商:CDE 制造商全稱:Cornell Dubilier Electronics 功能描述:Dipped, Radial Leaded, Solid Tantalum Capacitors |

| TDC274050NSE-F | 制造商:CDE 制造商全稱:Cornell Dubilier Electronics 功能描述:Dipped, Radial Leaded, Solid Tantalum Capacitors |

| TDC274K035NLE | 制造商:Mallory Sonalert Products Inc 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。