- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378684 > SAA7160ET (NXP Semiconductors N.V.) PCI Express based audio and video bridge PDF資料下載

參數(shù)資料

| 型號(hào): | SAA7160ET |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | PCI/cPCI/PXI |

| 英文描述: | PCI Express based audio and video bridge |

| 封裝: | SAA7160E/V2/R5<SOT879-1 (LBGA196)|<<http://www.nxp.com/packages/SOT879-1.html<1<Always Pb-free,;SAA7160ET/V2/R5<SOT951-1 (TFBGA88)|<<http://www.nxp.com/packages/SOT951-1. |

| 文件頁(yè)數(shù): | 42/57頁(yè) |

| 文件大小: | 236K |

| 代理商: | SAA7160ET |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)當(dāng)前第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)

SAA7160_1

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 01 — 25 February 2008

42 of 57

NXP Semiconductors

SAA7160

PCI Express based audio and video bridge

Any device addressed by a master is considered a slave. Generation of clock signals on

the I

2

C-bus is always the responsibility of the master device; each master generates its

own clock signals when transferring data on the bus. Bus clock signals from a master can

only be altered when they are stretched by a slow-slave device holding down the clock line

or by another master when arbitration occurs.

6.5 I

2

S-bus input interface

The SAA7160 has two independent audio slave interface circuits for serial input of digital

audio data streams. The audio interface circuits are based on the I

2

S-bus standard but

can be configured to several data and timing formats (with respect to framing, bit clock

and synchronization).

List of key features:

Supports

I

2

S-bus

, LSB and MSB justified formats

Sample size up to 32 bit

Standard stereo I

2

S-bus (MSB first, 1-bit delay from word select, left and right data in

a frame)

LSB first with 1-bit to 32-bits data per channel

Raw sample mode where the serial data for each active serial channel is sampled at

each sampling clock edge along with the word-select signal

Each of the slave I

2

S-bus interfaces consists two data lines, a word select line and a serial

clock line. The word select line distinguishes between the left and the right channel

information of the data lines. It is possible to sample up to 32 bits per channel, and there

are 4 channels on each module available.

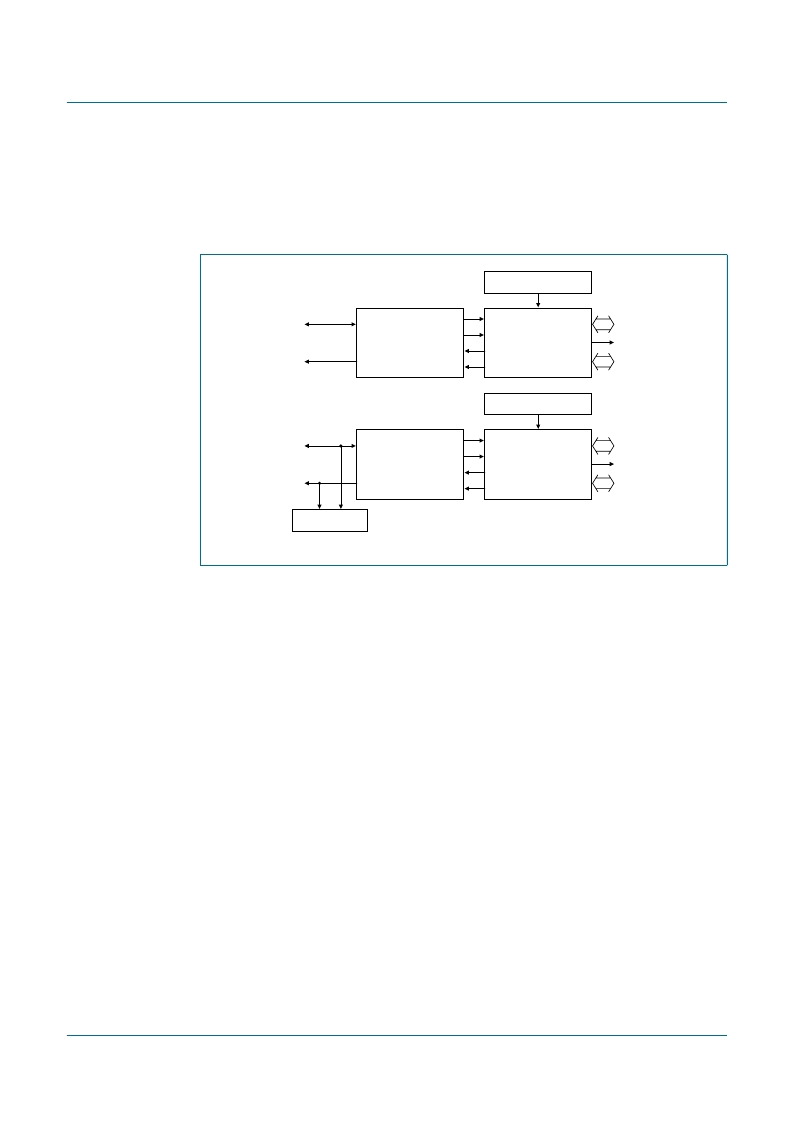

The following block diagram shows the structure of the different I

2

S-bus interfaces.

Fig 10. I

2

C-bus structure overview

001aag990

CLOCK GENERATOR

I

2

C-BUS

CORE 1

IN

OUT

data I

2

C-bus control

I

2

C-bus configuration

IRQ

SDA_A

SCL_A

global I

2

C-bus

BOOT EEPROM

I

2

C-BUS

INTERFACE 2

CLOCK GENERATOR

I

2

C-BUS

CORE 0

IN

OUT

data I

2

C-bus control

I

2

C-bus configuration

IRQ

SDA_B

SCL_B

global I

2

C-bus

I

2

C-BUS

INTERFACE 1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7706H | Car radio Digital Signal Processor (DSP) |

| SATURN | CDMA/AMPS dual Band IF Receiver for Digital Phones |

| SA | N-CHANNEL POWER MOSFET |

| SB12100 | Schottky Barrier Rectifiers |

| SB1220 | Schottky Barrier Rectifiers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7160ET/V2 | 制造商:NXP Semiconductors 功能描述:SAA7160ET/TFBGA88/TRAYDPM//V2 - Trays |

| SAA7160ET/V2,557 | 制造商:Sigma Designs 功能描述:PCI Express based audio and video bridge 88-Pin TFBGA |

| SAA7162E | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:PCI Express based dual channel multistandard audio and video decoder |

| SAA7164 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| SAA7165 | 制造商:NXP Semiconductors 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。