- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372114 > SAA7158 (NXP Semiconductors N.V.) Back END IC PDF資料下載

參數(shù)資料

| 型號(hào): | SAA7158 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Back END IC |

| 中文描述: | 后端芯片 |

| 文件頁(yè)數(shù): | 12/18頁(yè) |

| 文件大小: | 117K |

| 代理商: | SAA7158 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)

July 1994

12

Philips Semiconductors

Preliminary specification

Back END IC

SAA7158

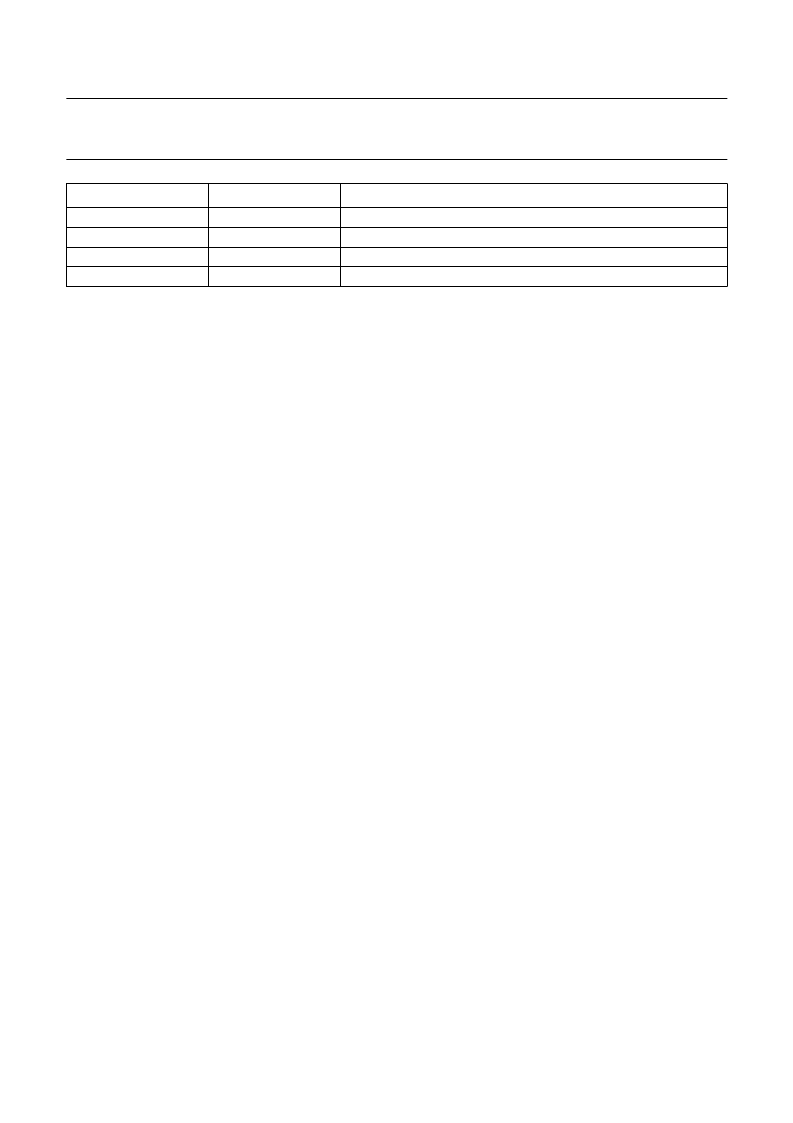

The function of the bits in the control datawords are explained below:

The BENDIC provides the correlation of two subsequent fields with its ‘Movie phase detector’ via the

μ

P interface. The

MSB or LSB values of this correlation factor is read from the BENDIC by sending an addressbyte and subsequently

receiving a databyte from it, according to Table 2.

7C

7D

7E

7F

multiplexer setting

multiplexer setting

multiplexer setting

multiplexer setting

SET select field1 OFF; select median OFF (all databits are dummy)

SET select field1 ON; select median OFF (all databits are dummy)

SET select field1 OFF; select median ON (all databits are dummy)

SET select field1 ON; select median ON (all databits are dummy)

feedback

4:4:4

Yclip

UVbin

UV8bit

invUV

grey(3:0)

bln_d(1:0)

re2_d(1:0)

re1_d(1:0)

inv_re2

inv_re1

zoom(4:0)

black16

pixrep

Ips

range(1:0)

gain(1:0)

coring(1:0)

av_w_med

BP(1:0)

WG(1:0)

BFB

HI: feedback output is 3-state enabled = outputs active

HI: YUV-4:4:4 mode selected instead of 4:1:1 mode

HI: Y signal after peaking is clipped and converted to 9-bit range

HI: UV signals are taken from input as binary signals instead 2’s complement

HI: UV signals are taken from input as 8-bit values instead of 7-bit

HI: UV signals are inverted before the DACs (outputs =

U and

V)

determines highest 4 bits in shade of grey in side panels

shifts the internal BLN signal from 0 to 3 clock pulses with respect to input

shifts 5 to 8 clock pulses the RE2 output signal versus input

shifts 5 to 8 clock pulses the RE1 output signal versus input, additionally influenced by zoom

HI: RE2 output is polarity reversed in relation to RE2 input

HI: RE1 output is polarity reversed in relation to RE1 input

determines vertical zoom factor, which is (32/zoom(4:0)); zoom(4:0) = 0 is equivalent to no zoom

HI: the Y signal value during the blanking period is 16 instead of 0

HI: side panels have the same Y, U and V as on the edge of the last video information

HI: functional test mode for line on line median on/off

determines maximum in CTI range of looking back/looking forward

determines gain of CTI function

determines coring level in Y peaking

enable average UV while median in Y (UV := 1/2

×

direct

+

1/2

×

delayed)

determines frequency response in Y peaking

determines weighted addition in Y peaking with 1 or 1/2 or 1/4 or 0

HI: determines bypass for BF1 in Y peaking

ADDRESS (HEX)

FUNCTION

BIT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7158WP | Back END IC |

| SAA7165 | Digital Video Encoder EURO-DENC2 |

| SAA7183AWP | RECTIFIER SBR DUAL 30A 100V 200A-ifsm 850mV-vf 0.1mA-ir TO-220AB 50/TUBE |

| SAA7183A | Digital Video Encoder EURO-DENC2 |

| SAA7167 | YUV-to-RGB Digital-to-Analog Converter DAC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7158WP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Back END IC |

| SAA7160E | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:PCI Express based audio and video bridge |

| SAA7160E/V1,557 | 制造商:NXP Semiconductors 功能描述: |

| SAA7160E/V2,557 | 制造商:NXP Semiconductors 功能描述: |

| SAA7160ET | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:PCI Express based audio and video bridge |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。