- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372113 > SAA7138 (NXP Semiconductors N.V.) The Digital Video Decoder/Encoder Modules(數(shù)字視頻譯碼器/編碼器模塊) PDF資料下載

參數(shù)資料

| 型號: | SAA7138 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | The Digital Video Decoder/Encoder Modules(數(shù)字視頻譯碼器/編碼器模塊) |

| 中文描述: | 數(shù)字視頻解碼器/編碼器模塊(數(shù)字視頻譯碼器/編碼器模塊) |

| 文件頁數(shù): | 29/53頁 |

| 文件大小: | 456K |

| 代理商: | SAA7138 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

Module System: 7128MOD2

Philips Semiconductors

29

Application Note

AN 97085

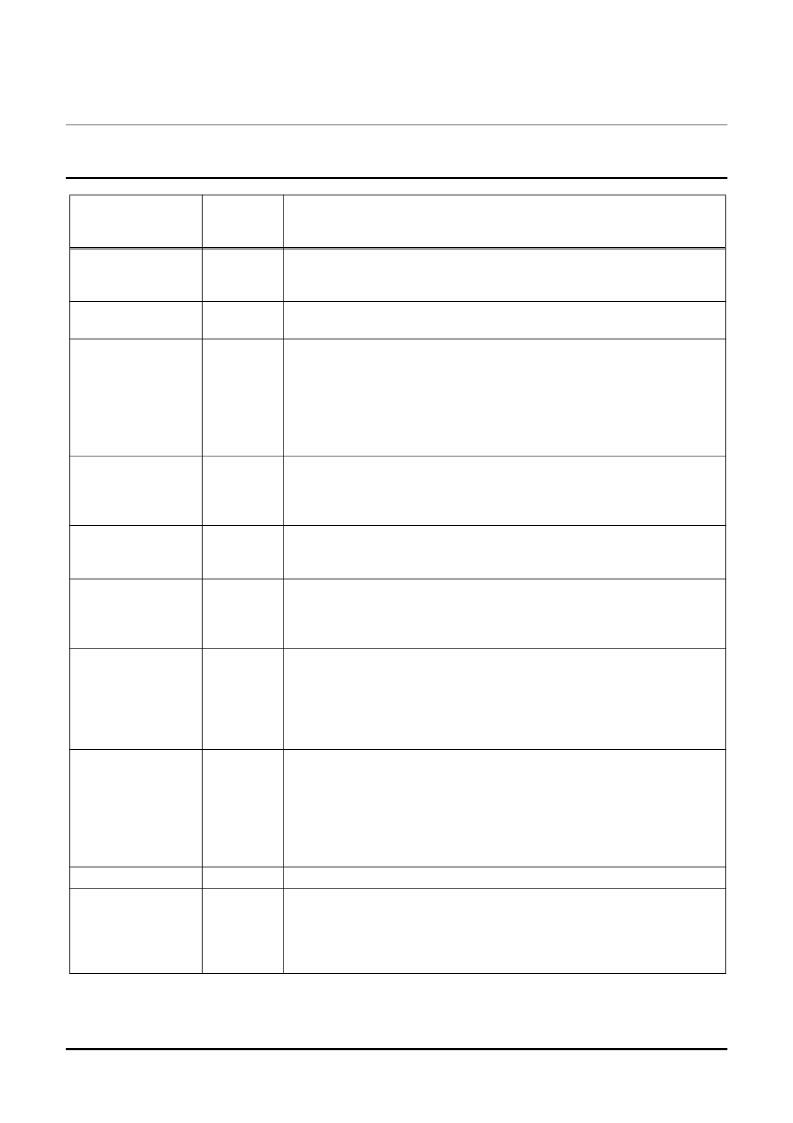

Line Select for Clo-

sed Caption or exten-

ded data

6FH

This parameter selects one out of 32 possible position for Closed Caption

encoding; usually it is line 21 for NTSC corresponding to 11h.

Start / End RCV2

70H - 72H

These registers define start and end of a pulse repeating at line frequency:

Note that if ’Start’ is greater than ’End’, the pulse will be inverted.

Every high-state of the signal at pin TTXRQ - depending on the chosen

Text format - initiates the transfer of a new Teletext bit stream bit; as this

bit stream must match to the internal pixel counter, the start of the first

request pulse is programmable by TTXHD to accomodate to indiviual lat-

encies of the bit stream source.

TTXHS is an internally needed parameter and should be taken as given in

the datasheet.

In master mode (RCV1 and RCV2 as outputs), sometimes the phase of

the horizontal pulse on RCV2 must be shifted against the phase of the ver-

tical sync pulse on RCV1 in steps of 27 MHz clock cycles. This can be

accomblished with this parameter in 3 steps.

In order to compensate for shorter propagation of RGB signals through a

TV SCART input, the alternative CSYNC signal on the (usually) CVBS

DAC can be advanced up to 31 LLC clock cycles.

For the odd and even field, the lines to carry Teletext information can be

determined individually.

Note that it is possible to nearly use the complete inactive and the com-

plete active fields for Teletext insertion instead of video.

These parameters define the Vertical Blanking Interval if bit SBLBN = low.

Main purpose is to widen the range for active video input, as the input data

are ignored during the lines that are dedicated to belong to the Vertical

Blanking Interval. E.g., Time code could be inserted through the video

input port when FAL is programmed to start before the normal first active

line.

TTXO set to low enables the universal TTX protocol: At every rising edge

of TTXRQ a single TTX bit is requested.

TTXO set to high enables the older TTX protocol for compatability rea-

sons: The encoder provides a high state window of TTXRQ, and the length

of the window depends on the chosen Text standard.

Depending on the selected field frequency (Bit FISE), the Teletext stan-

dard is being selected through TTX60

Always program with 00H in order to avoid unexpected effects

Starting with line line 8, ending with line 23 inclusive, each of these lines

can be disabled for Teletext insertion (the respective bit set to high),

although enabled by the global window definitions for Teletext. This can

be useful in order to allow e.g. other information entering through the video

input to be inserted between lines containing Teletext.

Start / DelayTTXRQ 73H - 74H

VSYNC shift

75H

CSYNC advanced

75H

TTX odd / even

request VS/VE

76H-79H,

7CH

First / Last

Active Line

7AH - 7CH

TTX mode

7CH

NULL

7DH

Disable TTX Line

7EH - 7FH

Function

SubAdr

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7140A | High Performance Scaler HPS |

| SAA7140B | High Performance Scaler HPS |

| SAA7146AHZ | Circular Connector; No. of Contacts:66; Series:MS27472; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:18; Circular Contact Gender:Pin; Circular Shell Style:Wall Mount Receptacle; Insert Arrangement:18-35 RoHS Compliant: No |

| SAA7146AH | .012UF/400VDC METAL POLY CAP |

| SAA7146A | Multimedia bridge, high performance Scaler and PCI circuit SPCI |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7140A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:High Performance Scaler HPS |

| SAA7140B | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:High Performance Scaler HPS |

| SAA7144HL | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Quadruple video input processor |

| SAA7145 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:PCI Multimedia Bridge |

| SAA7146 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。