- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372108 > SAA2023 (NXP Semiconductors N.V.) Drive processor for DCC systems PDF資料下載

參數(shù)資料

| 型號: | SAA2023 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Drive processor for DCC systems |

| 中文描述: | 戴納信貸驅(qū)動處理器的系統(tǒng) |

| 文件頁數(shù): | 26/56頁 |

| 文件大?。?/td> | 274K |

| 代理商: | SAA2023 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

May 1994

26

Philips Semiconductors

Preliminary specification

Drive processor for DCC systems

SAA2023

MEA717

100 %

91 %

50 %

9 %

0

duty

factor

speed

+ 2 blocks

+ 10.6 ms

+ 1.65 blocks

+ 8.8 ms

– 2 blocks

– 10.6 ms

– 1.65 blocks

– 8.8 ms

0

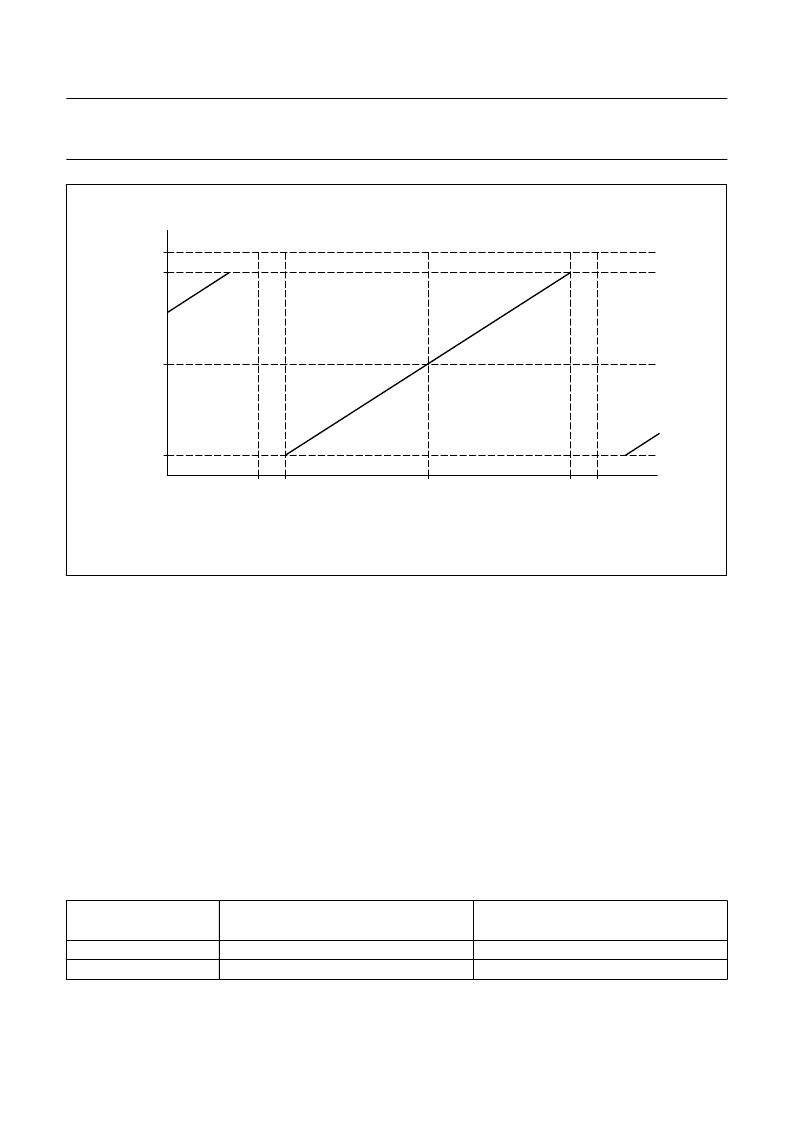

Fig.22 SPEED regulation duty factor as a function of phase characteristic.

If EnFReg is programmed ‘LOW’ then there is phase

regulation of the capstan speed. The period of the pulse

width modulated SPEED signal is 41.66

μ

s. The SAA2023

performs a new calculation to determine the duty factor of

SPEED once every 21.33 ms, giving a sampling rate of

approximately 46.9 Hz. This calculation is basically a

phase comparison between the incoming Main Data tape

frame and an internally generated reference. The SPEED

duty factor as a function of phase characteristic is shown

in Fig.22. As shown the duty factor increases

monotonously from approximately 9% when the incoming

Main Data tape frame is 1.65 tape blocks (8.8 ms) too

early up to 91% when it is 1.65 tape blocks (8.8 ms) too

late. Outside of a

±

2 tape blocks range the pulse width

characteristic overflows and repeats itself forming a

sawtooth pattern. The SAA2023 has an internal buffer of

±

8.8 ms outside of which the phase information is invalid.

If EnFReg is programmed ‘HIGH’ then the above

description is over-ridden with frequency information. If the

incoming main data bit rate deviation from the nominal

96000 bits/s rate is less than the Phase Only Threshold

(POT) then the control is as described above in the phase

control description. If the deviation is more than the

Frequency Only Threshold (FOT) then the SPEED

information is gated with the phase information resulting in

the SPEED signal being continuously HIGH or LOW while

the condition continues. If the deviation is between the

POT and the FOT then the frequency information is gated

with the Phase information for 50% of the time.

The deviation thresholds POT and FOT are programmable

via the TFE settings bit SeINBand.

Table 20

POT and FOT deviation thresholds.

SeINBand

POT

(DEVIATION FROM NOMINAL)

±

6%

±

3%

FOT

(DEVIATION FROM NOMINAL)

±

9%

±

4.5%

0

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA2023H | RES 4.53K OHM 1/16W 0.5% 0402SMD |

| SAA2500 | MPEG Audio Source Decoder |

| SAA2500H | MPEG Audio Source Decoder |

| SAA2501 | Digital Audio Broadcast DAB decoder |

| SAA2501H | Digital Audio Broadcast DAB decoder |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA2023GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Drive processor for DCC systems |

| SAA2023H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Drive processor for DCC systems |

| SAA2032 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital equalization for the tape drive processing of the DCC system |

| SAA2032GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital equalization for the tape drive processing of the DCC system |

| SAA-21 | 制造商:GENERAL DEVICES 功能描述:CHASSIS SUPPORT ANGLES, Sold in a Set of 2 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。