- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368096 > PPC440GR-3pbfffCx (Applied Micro Circuits Corp.) Power PC 440GR Embedded Processor PDF資料下載

參數(shù)資料

| 型號: | PPC440GR-3pbfffCx |

| 廠商: | Applied Micro Circuits Corp. |

| 英文描述: | Power PC 440GR Embedded Processor |

| 中文描述: | 440GR的Power PC嵌入式處理器 |

| 文件頁數(shù): | 79/82頁 |

| 文件大小: | 527K |

| 代理商: | PPC440GR-3PBFFFCX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁當(dāng)前第79頁第80頁第81頁第82頁

AMCC Proprietary

79

440GR – PPC440GR Embedded Processor

Preliminary Data Sheet

Revision 1.16 – July 19, 2006

Initialization

The PPC440GR provides the option for setting initial parameters based on default values or by reading them from

a slave PROM attached to the IIC0 bus (see “Serial EEPROM” below). Some of the default values can be altered

by strapping on external pins (see “Strapping” below).

Strapping

While the SysReset input pin is low (system reset), the state of certain I/O pins is read to enable certain default

initial conditions prior to PPC440GR start-up. The actual capture instant is the nearest reference clock edge before

the deassertion of reset. These pins must be strapped using external pull-up (logical 1) or pull-down (logical 0)

resistors to select the desired default conditions. These pins are used for strap functions only during reset.

Following reset they are used for normal functions. The signal names assigned to the pins for normal operation are

shown in parentheses following the pin number.

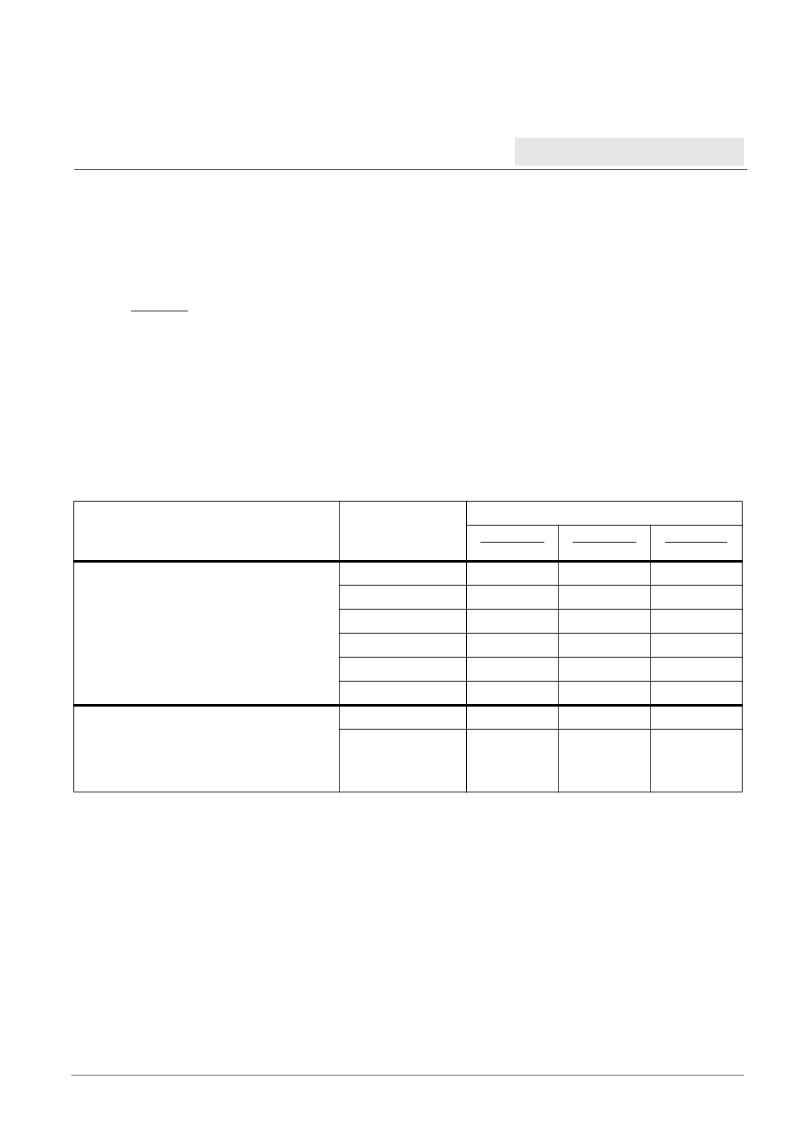

The following table lists the strapping pins along with their functions and strapping options:

Serial EEPROM

During reset, initial conditions other than those obtained from the strapping pins can be read from a ROM device

connected to the IIC0 port. At the de-assertion of reset, if the bootstrap controller is enabled, the PPC440GR

sequentially reads 16B from the ROM device on the IIC0 port and sets the SDR0_SDSTP0, SDR0_SDSTP1,

SDR0_SDSTP2 and SDR0_SDSTP3 registers accordingly.

The initialization settings and their default values are covered in detail in the

PowerPC 440GR User’s Manual

.

Table 24. Strapping Pin Assignments

Function

Option

Ball Strapping

R25

(UART0_DCD)

U26

(UART0_DSR)

V26

(UART0_CTS)

Serial device is disabled. Each of the six options (A–

F) is a combination of boot source, boot-source

width, and clock frequency specifications. Refer to

the IIC Bootstrap Controller chapter in the

PPC440GR Embedded Processor User’s Manual

for

details.

A

0

0

0

B

0

0

1

C

0

1

0

D

0

1

1

E

1

0

0

F

1

1

0

Serial device is enabled. The option being selected is

the IIC0 slave address that will respond with

strapping data.

Note:

If reading of configuration data from the serial

device fails, the PPC440GR defaults to configuration

X.

G (0xA8)

1

0

1

H (0xA4)

1

1

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PPC440GRx-NpAfffTs | PowerPC 440GRx Embedded Processor |

| PPC440GRx-SpAfffTs | PowerPC 440GRx Embedded Processor |

| PPC440GX-3RF800CZ | Power PC 440GX Embedded Processor |

| PPC440GX-3CC533S | Power PC 440GX Embedded Processor |

| PPC440GX-3CC667S | Power PC 440GX Embedded Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PPC440GRX-NPAFFFTS | 制造商:AMCC 制造商全稱:Applied Micro Circuits Corporation 功能描述:PowerPC 440GRx Embedded Processor |

| PPC440GRX-NTA400E | 制造商:AMCC 功能描述:32 BIT POWERPC CORE, UP TO 667 MHZ, 2 10/100/1000 ETHERNET, - Trays |

| PPC440GRX-NTA400EZ | 制造商:AMCC 功能描述:32 BIT POWERPC CORE, UP TO 667 MHZ, 2 10/100/1000 ETHERNET, - Tape and Reel |

| PPC440GRX-NTA533EZ | 制造商:AMCC 功能描述:32 BIT POWERPC CORE, UP TO 667 MHZ, 2 10/100/1000 ETHERNET, - Tape and Reel |

| PPC440GRX-NTA667EZ | 制造商:AMCC 功能描述:32 BIT POWERPC CORE, UP TO 667 MHZ, 2 10/100/1000 ETHERNET, - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。