- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378055 > PM7329-BI (PMC-SIERRA INC) ATM TRAFFIC MANAGER AND SWITCH PDF資料下載

參數(shù)資料

| 型號(hào): | PM7329-BI |

| 廠商: | PMC-SIERRA INC |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | ATM TRAFFIC MANAGER AND SWITCH |

| 中文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA352 |

| 封裝: | 35 X 35 MM, 1.45 MM HEIGHT, SBGA-352 |

| 文件頁(yè)數(shù): | 65/232頁(yè) |

| 文件大小: | 1585K |

| 代理商: | PM7329-BI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)當(dāng)前第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)第223頁(yè)第224頁(yè)第225頁(yè)第226頁(yè)第227頁(yè)第228頁(yè)第229頁(yè)第230頁(yè)第231頁(yè)第232頁(yè)

PM7329 S/UNI-APEX-1K800

DATASHEET

PMC-2010141

ISSUE 2

ATM TRAFFIC MANAGER AND SWITCH

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

51

knowledge of which polling addresses are associated with devices and which are

associated with ports is not required.

If UL2M or Any-PHY, and the number of ports connected is less than 32 (loop) or

4 (WAN), there is an option of limiting the polling range; thereby providing

optimal polling efficiency.

The UL1M is effectively a UL2M without address polling, but retains the port

selection handshake. Hence a single external UL2S may be connected to the

S/UNI-APEX-1K800 UL1M transmit interface.

If Any-PHY, the S/UNI-APEX-1K800 expects the Any-PHY slave device to act as

a proxy for its internal ports. The S/UNI-APEX-1K800 places no restrictions on

the number of internal ports within an Any-PHY slave device. Since the polling is

tied to the data transfer, both the WAN and loop Any-PHY receive interface is

capable of mixing prepend enabled UL2 and Any-PHY slaves on the same bus

with some external glue logic.

If UL2S, the S/UNI-APEX-1K800 operates as a single port UTOPIA L2 transmit

slave port. The address pins become inputs and can be configured to respond to

any port identifier from 0 to 31 for loop, and 0 to 3 for WAN.

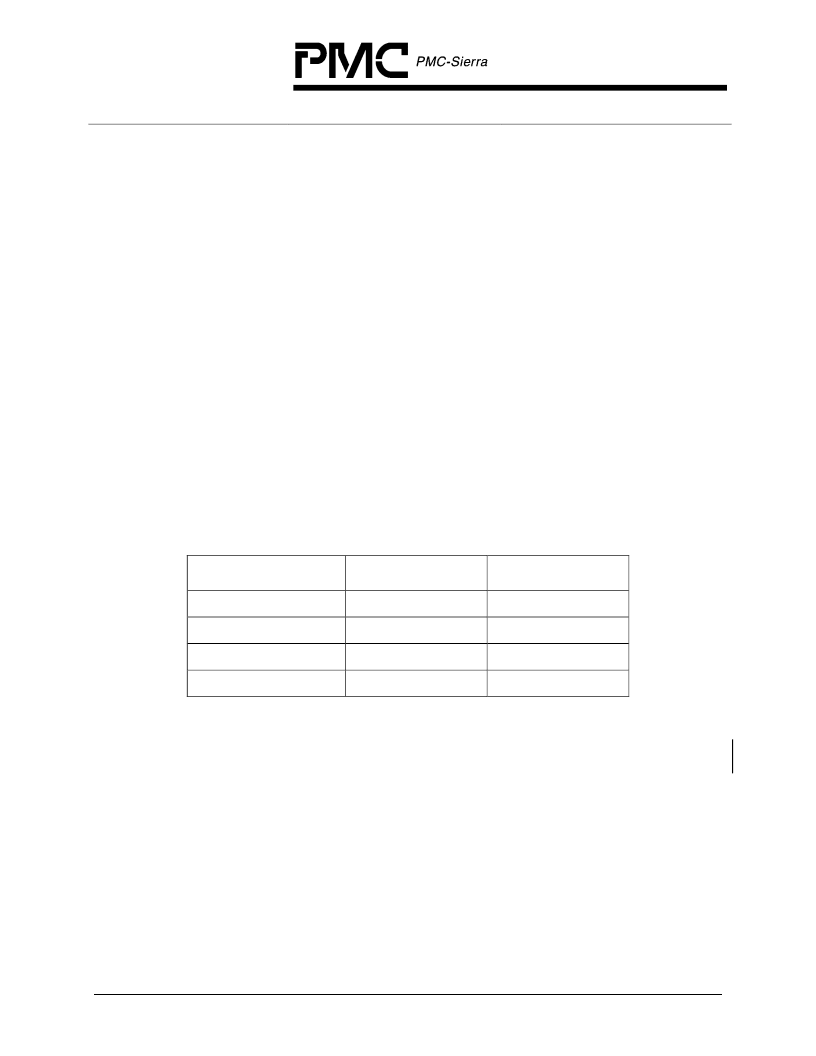

Table 4

- Number of Ports Supported, Receive Interface

Mode

Loop (8/16bit)

WAN (8/16bit)

Any-PHY Master

32

4

UTOPIA L2 Master

32

4

UTOPIA L1 Master

1

1

UTOPIA L2 Slave

1 of 32

1 of 4

10.1.2 Transmit Interface

The Transmit Cell Transfer Format is shown in Figure 6 and Figure 7. Word/byte

0 is required for cell transfers to Any-PHY slaves. The address prepend is the

S/UNI-APEX-1K800 port id associated with the transmit queue in which the cell

was en-queued. The unused bits in the address prepend are reserved and

devices should not rely on the content. Optional word 1 or bytes {1,2} enables

the prepending of a 16-bit switch tag. Optional word 2 or bytes {3,4} enables the

prepending of a 16-bit Egress Connection Identifier (ECI). Both the Switch tag

and the Egress Connection Identifier are sourced on a per-VC basis from VC

context. The S/UNI-APEX-1K800 also maps the ECI tag to the HEC/UDF field

(word 5) for 16-bit transfer. Word 5 or byte 9 is optional. The S/UNI-APEX-1K800

supports optional VPI and/or VCI mapping, selectable on a per VC basis.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PM7329 | ATM TRAFFIC MANAGER AND SWITCH |

| PM7339 | Quad Cell Delineation Block Device |

| PM7340 | S/UNI INVERSE MULTIPLEXING FOR ATM, 8 LINKS |

| PM7340-PI | SCREW,WING |

| PM7341 | S/UNI INVERSE MULTIPLEXING FOR ATM, 84 LINKS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PM733 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| PM7339 | 制造商:PMC 制造商全稱:PMC 功能描述:SATURN USER NETWORK INTERFACE CELL DELINEATION BLOCK |

| PM734 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| PM7340 | 制造商:PMC 制造商全稱:PMC 功能描述:S/UNI INVERSE MULTIPLEXING FOR ATM, 8 LINKS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。