- 您現在的位置:買賣IC網 > PDF目錄369960 > PDI1394P25EC (NXP SEMICONDUCTORS) 1-port 400 Mbps physical layer interface PDF資料下載

參數資料

| 型號: | PDI1394P25EC |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1-port 400 Mbps physical layer interface |

| 中文描述: | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PBGA64 |

| 封裝: | 8 X 8 X 1.05 MM, PLASTIC, LFBGA-64 |

| 文件頁數: | 38/42頁 |

| 文件大小: | 233K |

| 代理商: | PDI1394P25EC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當前第38頁第39頁第40頁第41頁第42頁

Philips Semiconductors

Preliminary data

PDI1394P23

2-port/1-port 400 Mbps physical layer interface

2001 Sep 06

38

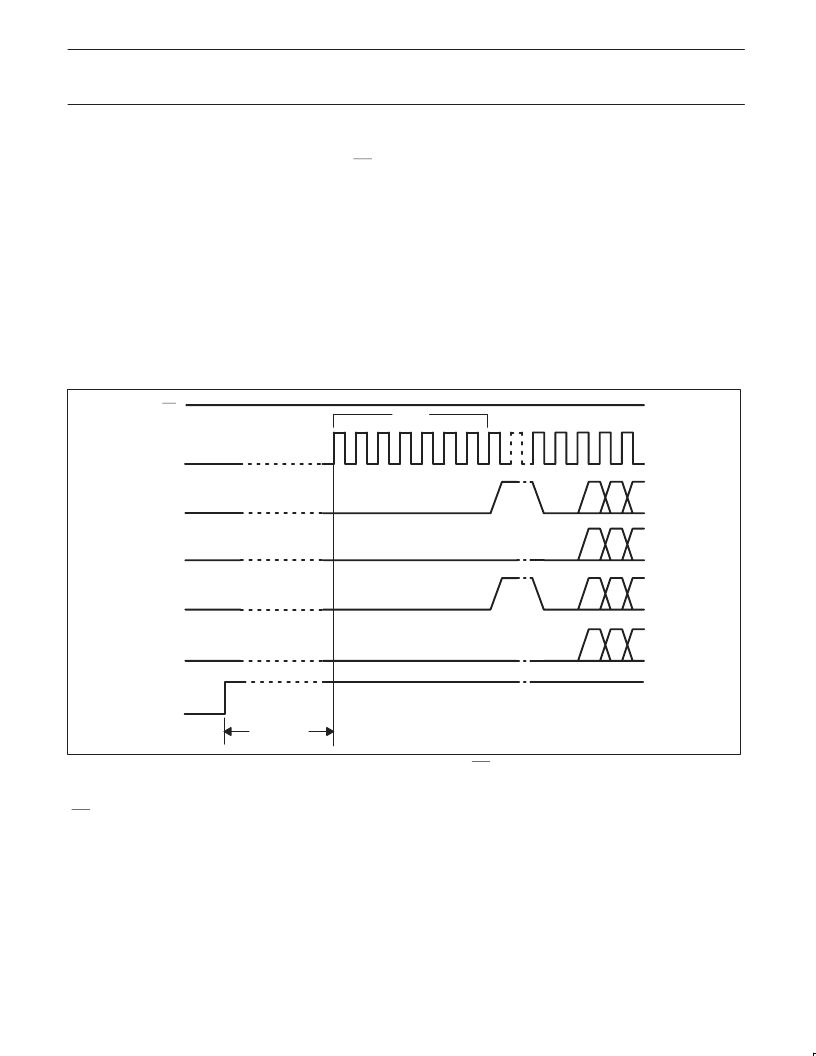

The sequence of events for initialization of the PHY-LLC interface

when the interface is in the differentiated mode of operation (ISO

terminal is low) is as follows:

1. LPS reasserted. After the interface has been in the reset or

disabled state for at least the minimum T

RESTORE

time, the LLC

causes the interface to be initialized and restored to normal

operation by re-activating the LPS signal. (In the above diagram,

the interface is shown in the disabled state with SYSCLK

high-impedance inactive. However, the interface initialization

sequence described here is also executed if the interface is

merely reset but not yet disabled.)

2. SYSCLK activated. If the interface is disabled, the PHY

re-activates its SYSCLK output when it detects that LPS has

been reasserted. SYSCLK will be restored within 60 ns. The

PHY commences SYSCLK activity by driving the SYSCLK

output low for half a cycle. Thereafter, the SYSCLK output is a

50% duty cycle square wave with a frequency of 49.152 MHz

+100 ppm (period of 20.345 ns). Upon the first full cycle of

SYSCLK, the PHY drives the CTL and D terminals low for one

cycle. The LLC is also required to drive its CTL, D, and LREQ

outputs low during one of the first six cycles of SYSCLK (in the

above diagram, this is shown as occurring in the first SYSCLK

cycle).

3. Receive indicated. Upon the eighth SYSCLK cycle following

reassertion of LPS, the PHY asserts the Receive state on the

CTL lines and the data-on indication (all ones) on the D lines for

one or more cycles (because the interface is in the differentiated

mode of operation, the CTL and D lines will be in the

high-impedance state after the first cycle).

4. Initialization complete. The PHY asserts the Idle state on the

CTL lines and logic 0 on the D lines. This indicates that the

PHY-LLC interface initialization is complete and normal

operation may commence. The PHY will now accept requests

from the LLC via the LREQ line.

T

CLK_ACTIVATE

CTL0

LPS

SV01815

ISO

SYSCLK

D0 – D7

LREQ

(high)

(c)

7 cycles

(b)

CTL1

(a)

Figure 25.

Interface Initialization, ISO High

The sequence of events for initialization of the PHY-LLC interface

when the interface is in the non-differentiated mode of operation

(ISO terminal is high) is as follows:

1. LPS reasserted. After the interface has been in the reset or

disabled state for at least the minimum T

RESTORE

time, the LLC

causes the interface to be initialized and restored to normal

operation by reasserting the LPS signal. (In the above diagram,

the interface is shown in the disabled state with SYSCLK low

inactive. However, the interface initialization sequence described

here is also executed if the interface is merely reset but not yet

disabled.)

2. SYSCLK activated. If the interface is disabled, the PHY

re-activates its SYSCLK output when it detects that LPS has

been reasserted. SYSCLK will be restored within 60 ns. The

SYSCLK output is a 50% duty cycle square wave with a

frequency of 49.152 MHz +100 ppm (period of 20.345 ns).

During the first seven cycles of SYSCLK, the PHY continues to

drive the CTL and D terminals low. The LLC is also required to

drive its CTL and D outputs low for one of the first six cycles of

SYSCLK but to otherwise place its CTL and D outputs in a

high-impedance state. The LLC continues to drive its LREQ

output low during this time.

3. Receive indicated. Upon the eighth SYSCLK cycle following

reassertion of LPS, the PHY asserts the Receive state on the

CTL lines and the data-on indication (all ones) on the D lines for

one or more cycles.

4. Initialization complete. The PHY asserts the Idle state on the

CTL lines and logic 0 on the D lines. This indicates that the

PHY-LLC interface initialization is complete and normal

operation may commence. The PHY will now accept requests

from the LLC via the LREQ line.

相關PDF資料 |

PDF描述 |

|---|---|

| PDI1394P23BD | 2-port/1-port 400 Mbps physical layer interface |

| PDI1394L41BE | 8358 PBGA ENCRP NO-PB |

| PDI1394P21BE | 3-port physical layer interface |

| PDI1394P22BD | 3-port physical layer interface |

| PDI1394L11BA | 1394 AV link layer controller |

相關代理商/技術參數 |

參數描述 |

|---|---|

| PDI-15R | 制造商:Power Dynamics Inc 功能描述: |

| PDI-15RH-5 | 制造商:Power Dynamics Inc 功能描述: |

| PDI-15RH-5-R-G30 | 制造商:Power Dynamics Inc 功能描述:PDI Series 15 Position Right Angle Socket High Density D-Sub |

| PDI-15S | 制造商:POWER DYNAMICS 功能描述: 制造商:Power Dynamics Inc 功能描述: |

| PDI-15SH | 制造商:Power Dynamics Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。