- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369960 > PDI1394P25EC (NXP SEMICONDUCTORS) 1-port 400 Mbps physical layer interface PDF資料下載

參數(shù)資料

| 型號: | PDI1394P25EC |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1-port 400 Mbps physical layer interface |

| 中文描述: | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PBGA64 |

| 封裝: | 8 X 8 X 1.05 MM, PLASTIC, LFBGA-64 |

| 文件頁數(shù): | 32/42頁 |

| 文件大?。?/td> | 233K |

| 代理商: | PDI1394P25EC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Philips Semiconductors

Preliminary data

PDI1394P23

2-port/1-port 400 Mbps physical layer interface

2001 Sep 06

32

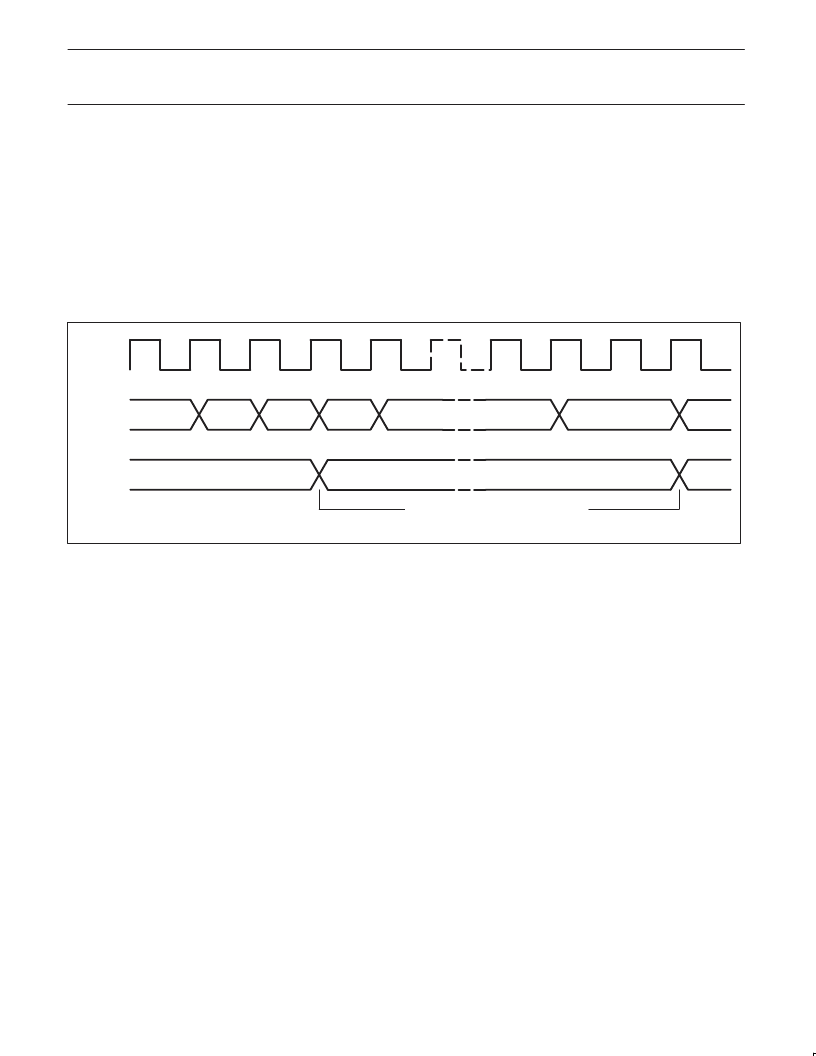

The sequence of events for a cancelled/null packet transmission is

as follows:

Transmit operation initiated. PHY asserts grant on the CTL lines

followed by idle to hand over control of the interface to the link.

Optional Idle cycle. The link may assert at most one idle cycle

preceding assertion of hold. This idle cycle is optional; the link is

not required to assert idle preceding Hold.

Optional Hold cycles. The link may assert Hold for up to 47 cycles

preceding assertion of idle. These hold cycle(s) are optional; the

link is not required to assert hold preceding Idle.

Null transmit termination. The null transmit operation is terminated

by the link asserting two cycles of idle on the CTL lines and then

releasing the interface and returning control to the PHY. Note that

the link may assert Idle for a total of 3 consecutive cycles if it

asserts the optional first idle cycle but does not assert hold. It is

recommended that the link assert 3 cycles of Idle to cancel a

packet transmission if no hold cycles are asserted. This ensures

that either the link or PHY controls the interface in all cycles.

After regaining control of the interface, the PHY shall assert at

least one cycle of Idle before any subsequent status transfer,

receive operation, or transmit operation.

SYSCLK

(a)

CTL0, CTL1

D0–D7

00

00

01

SV01763

Link Controls Ctl and D

PHY High-impedance Ctl and D Outputs

00

11

00

(b)

(c)

(d)

(e)

00

00

00

00

Figure 19.

Cancelled/Null Packet Transmission

18.5

The LLC controls the state of the PHY-LLC interface using the LPS

signal. The interface may be placed into a reset state, a disabled

state, or be made to initialize and then return to normal operation.

When the interface is not operational (whether reset, disabled, or in

the process of initialization) the PHY cancels any outstanding bus

request or register read request, and ignores any requests made via

the LREQ line. Additionally, any status information generated by the

PHY will not be queued and will not cause a status transfer upon

restoration of the interface to normal operation.

Interface reset and disable

The LPS signal may be either a level signal or a pulsed signal,

depending upon whether the PHY–LLC interface is a direct

connection or is made across an isolation barrier. When an isolation

barrier exists between the PHY and LLC (whether of the Philips

bus-holder type or Annex J type) the LPS signal must be pulsed. In

a direct connection, the LPS signal may be either a pulsed or a level

signal. Timing parameters for the LPS signal are given in Table 20.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PDI1394P23BD | 2-port/1-port 400 Mbps physical layer interface |

| PDI1394L41BE | 8358 PBGA ENCRP NO-PB |

| PDI1394P21BE | 3-port physical layer interface |

| PDI1394P22BD | 3-port physical layer interface |

| PDI1394L11BA | 1394 AV link layer controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PDI-15R | 制造商:Power Dynamics Inc 功能描述: |

| PDI-15RH-5 | 制造商:Power Dynamics Inc 功能描述: |

| PDI-15RH-5-R-G30 | 制造商:Power Dynamics Inc 功能描述:PDI Series 15 Position Right Angle Socket High Density D-Sub |

| PDI-15S | 制造商:POWER DYNAMICS 功能描述: 制造商:Power Dynamics Inc 功能描述: |

| PDI-15SH | 制造商:Power Dynamics Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。