- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369948 > PC28F256J3C-110 (Intel Corp.) Intel StrataFlash Memory (J3) PDF資料下載

參數(shù)資料

| 型號(hào): | PC28F256J3C-110 |

| 廠商: | Intel Corp. |

| 英文描述: | Intel StrataFlash Memory (J3) |

| 中文描述: | 英特爾StrataFlash存儲(chǔ)器(J3) |

| 文件頁(yè)數(shù): | 55/72頁(yè) |

| 文件大?。?/td> | 905K |

| 代理商: | PC28F256J3C-110 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)當(dāng)前第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)

256-Mbit J3 (x8/x16)

Datasheet

55

A.5

System Interface Information

The following device information can optimize system interface software.

A.6

Device Geometry Definition

This field provides critical details of the flash device geometry.

0000h means no second vendor-specified algorithm exists

Secondary algorithm Extended Query Table address.

0000h means none exists

18:

19:

1A:

--00

--00

--00

19h

2

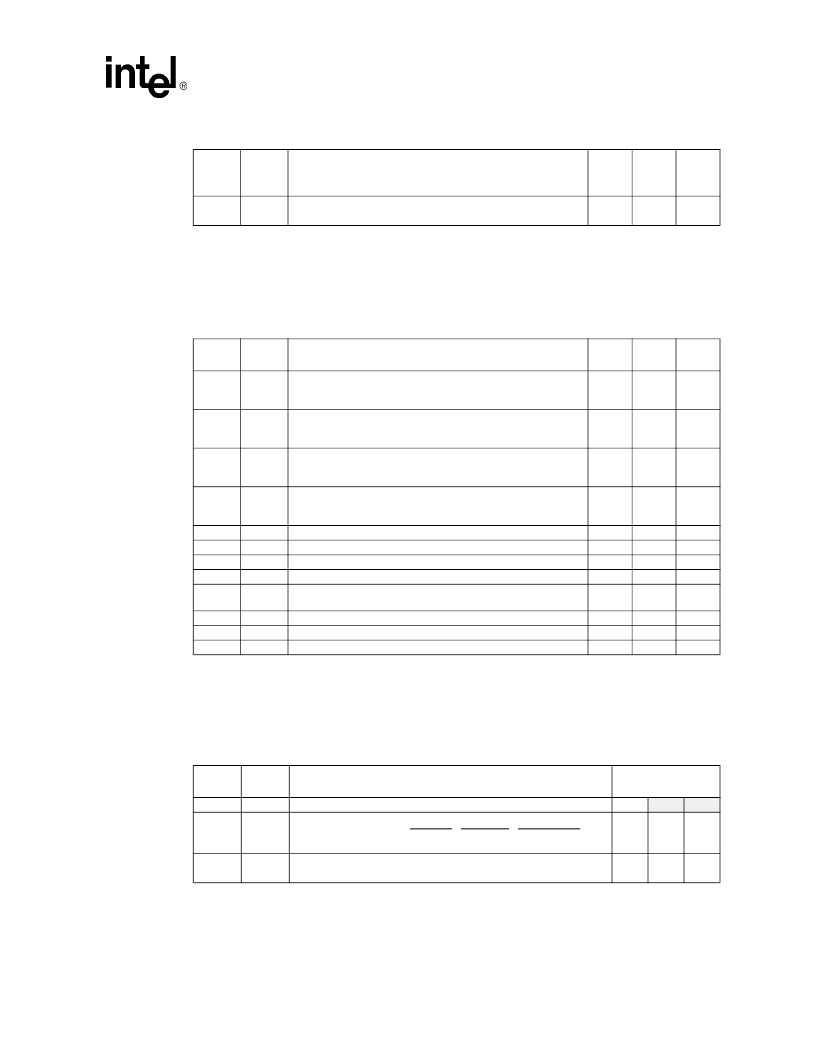

Table 27. CFI Identification (Sheet 2 of 2)

Offset

Length

Description

Add.

Hex

Code

Value

Table 28. System Interface Information

Offset

Length

Description

Add.

Hex

Code

Value

1Bh

1

V

logic supply minimum program/erase voltage

bits 0–3 BCD 100 mV

bits 4–7 BCD volts

V

logic supply maximum program/erase voltage

bits 0–3 BCD 100 mV

bits 4–7 BCD volts

V

PP

[programming] supply minimum program/erase voltage

bits 0–3 BCD 100 mV

bits 4–7 HEX volts

V

[programming] supply maximum program/erase voltage

bits 0–3 BCD 100 mV

bits 4–7 HEX volts

“n” such that typical single word program time-out = 2

n

μs

“n” such that typical max. buffer write time-out = 2

n

μs

“n” such that typical block erase time-out = 2

n

ms

“n” such that typical full chip erase time-out = 2

n

ms

“n” such that maximum word program time-out = 2

n

times

typical

“n” such that maximum buffer write time-out = 2

n

times typical

“n” such that maximum block erase time-out = 2

n

times typical

“n” such that maximum chip erase time-out = 2

n

times typical

1B:

--27

2.7 V

1Ch

1

1C:

--36

3.6 V

1Dh

1

1D:

--00

0.0 V

1Eh

1

1E:

--00

0.0 V

1Fh

20h

21h

22h

1

1

1

1

1F:

20:

21:

22:

--08

--08

--0A

--00

256 μs

256 μs

1 s

NA

23h

1

23:

--04

2 ms

24h

25h

26h

1

1

1

24:

25:

26:

--04

--04

--00

2 ms

16 s

NA

Table 29. Device Geometry Definition (Sheet 1 of 2)

Offset

Length

Description

Code See Table

Below

27:

27h

1

“n” such that device size = 2

n

in number of bytes

28h

2

Flash device interface: x8 async x16 async x8/x16 async

28:

--02

x8/

x16

28:00,29:00 28:01,29:00 28:02,29:00

“n” such that maximum number of bytes in write buffer = 2

n

29:

2A:

2B:

--00

--05

--00

2Ah

2

32

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PC28F128J3C-110 | Intel StrataFlash Memory (J3) |

| PC28F640J3C-110 | Intel StrataFlash Memory (J3) |

| PC28F320J3C-110 | Intel StrataFlash Memory (J3) |

| PC28F320J3A-110 | Intel StrataFlash Memory (J3) |

| PC28F320J3A-115 | Intel StrataFlash Memory (J3) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PC28F256J3C-115 | 制造商:INTEL 制造商全稱(chēng):Intel Corporation 功能描述:Intel StrataFlash Memory (J3) |

| PC28F256J3C-120 | 制造商:INTEL 制造商全稱(chēng):Intel Corporation 功能描述:Intel StrataFlash Memory (J3) |

| PC28F256J3C125 | 制造商:INTEL 制造商全稱(chēng):Intel Corporation 功能描述:Intel StrataFlash?? Memory |

| PC28F256J3C-125 | 制造商:INTEL 制造商全稱(chēng):Intel Corporation 功能描述:Intel StrataFlash Memory (J3) |

| PC28F256J3C125 S B93 | 制造商:Intel 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。