- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369945 > PA28F002BC-T80 (INTEL CORP) 28F002BC 2-MBIT (256K X 8) BOOT BLOCK FLASH MEMORY PDF資料下載

參數(shù)資料

| 型號: | PA28F002BC-T80 |

| 廠商: | INTEL CORP |

| 元件分類: | PROM |

| 英文描述: | 28F002BC 2-MBIT (256K X 8) BOOT BLOCK FLASH MEMORY |

| 中文描述: | 256K X 8 FLASH 12V PROM, 80 ns, PDSO44 |

| 封裝: | 0.525 X 1.110 INCH, PLASTIC, SOP-44 |

| 文件頁數(shù): | 15/37頁 |

| 文件大小: | 455K |

| 代理商: | PA28F002BC-T80 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

E

28F002BC 2-MBIT BOOT BLOCK FLASH MEMORY

15

PRELIMINARY

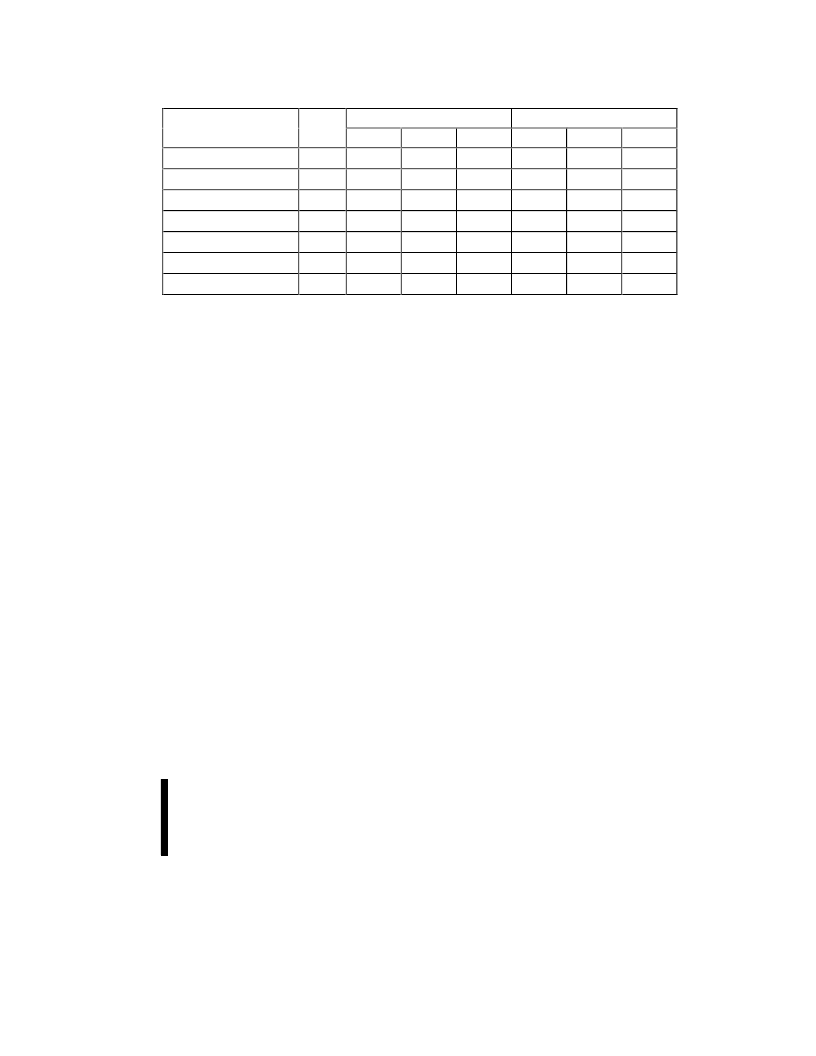

Table 4. Command Bus Definitions

First Bus Cycle

Second Bus Cycle

Command

Notes

Oper

Addr

Data

Oper

Addr

Data

Read Array

Write

X

FFH

Intelligent Identifier

1,2

Write

X

90H

Read

IA

IID

Read Status Register

Write

X

70H

Read

X

SRD

Clear Status Register

Write

X

50H

Program Setup

Write

PA

40H

Write

PA

PD

Block Erase/Confirm

Write

BA

20H

Write

BA

D0H

Erase Suspend/Resume

Write

X

B0H

Write

X

D0H

ADDRESS

BA = Block Address

IA = Identifier Address

PA = Program Address

X = Don’t Care

DATA

SRD = Status Register Data

IID = Intelligent Identifier Data

PD = Program Data

NOTES:

1.

Bus operations are defined in Table 2.

2.

Following the Intelligent Identifier command, two read operations access manufacturer and device codes respectively.

3.3.1.1

Command Function Description

Device operations are selected by writing specific

commands into the CUI. Tables 3 and 4 define the

available commands. Status Register (SR) bits are

defined in Table 5.

Invalid/Reserved

These are unassigned commands and should not

be used. Intel reserves the right to redefine these

codes for future functions.

Read Array (FFH)

This single write cycle command points the read

path at the array. If the host CPU performs a

CE#/OE#-controlled Read immediately following a

two-write sequence (i.e., a Program or Erase

command) that started the WSM, then the device

will output status register contents. Writing two

Read Array (FFH) commands to the CUI aborts the

current operation and resets to read array mode.

Executing Read Array after the Erase Setup

command (instead of giving Erase Confirm) causes

the status register Erase and Program Status bits to

be set. This indicates that an erase operation was

initiated but not successfully confirmed (an Erase

Confirm at this point would be ignored by the CUI).

A subsequent Read Array command will point the

data path at the array (see Appendix B).

Intelligent Identifier (90H)

After this command is executed, the CUI points the

output path to the intelligent identifier circuits. Only

intelligent identifier values at addresses 0 and 1 can

be read (only address A

0

is used in this mode; all

other address inputs are ignored).

相關PDF資料 |

PDF描述 |

|---|---|

| PA28F008SA-85 | 8-MBIT (1-MBIT x 8) FlashFileTM MEMORY |

| PA28F008SC-85 | BYTE-WIDE SmartVoltage FlashFile MEMORY FAMILY 4, 8, AND 16 MBIT |

| PA28F008SA-120 | 8-MBIT (1-MBIT x 8) FlashFileTM MEMORY |

| PA28F008SC-120 | BYTE-WIDE SmartVoltage FlashFile MEMORY FAMILY 4, 8, AND 16 MBIT |

| PA34 | POWER OPERATIONAL AMPLIFIERS |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PA28F004S3-120 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:BYTE-WIDE SMART 3 FlashFile MEMORY FAMILY 4, 8, AND 16 MBIT |

| PA28F004S3-150 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:BYTE-WIDE SMART 3 FlashFile MEMORY FAMILY 4, 8, AND 16 MBIT |

| PA28F004S5-120 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:BYTE-WIDE SMART 5 FlashFile MEMORY FAMILY 4, 8, AND 16 MBIT |

| PA28F004S5-85 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:BYTE-WIDE SMART 5 FlashFile MEMORY FAMILY 4, 8, AND 16 MBIT |

| PA28F004SC-120 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:BYTE-WIDE SmartVoltage FlashFile⑩ MEMORY FAMILY 4, 8, AND 16 MBIT |

發(fā)布緊急采購,3分鐘左右您將得到回復。