- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369945 > P8XC557E8 (NXP Semiconductors N.V.) 8 BIT MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號: | P8XC557E8 |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 8位微控制器 |

| 英文描述: | 8 BIT MICROCONTROLLER |

| 中文描述: | 8位微控制器 |

| 文件頁數(shù): | 50/84頁 |

| 文件大小: | 322K |

| 代理商: | P8XC557E8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁當(dāng)前第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

1999 Mar 12

50

Philips Semiconductors

Product specification

8-bit microcontroller

P8xC557E8

16.2.4

S

ECONDS

T

IMER

This counter provides an overflow signal every second,

when the 32 kHz oscillator is running. The overflow output

sets the interrupt flag SECINT. This interrupt can be

disabled/enabled by ENSECI. If SECINT is enabled, it is

logically ORed with INT1 (External interrupt 1).

The ‘seconds’ interrupt andINT1 therefore share the same

priority and vector. The software has to check both flags

SECINT (PLLCON.5) and IE1 (TCON.3) to distinguish

between the two interrupt sources. SECINT can only be

cleared via writing a logic 0 to this bit.

The external interruptsINT0,INT1 or the seconds interrupt

can wake-up the PLL oscillator and the microcontroller as

described in Chapter 15.3. For a wake-up via INT1 or

seconds interrupt, IE1 must be enabled and

level-sensitive.

A further function of the seconds timer is to control the

start-up timing of the microcontroller after reset or after

wake-up from Power-down.

It controls the stretching of the reset pulse to the

microcontroller and controls releasing the system clock to

the microcontroller. A RSTIN signal of 1

μ

s at minimum will

reset the microcontroller.

In the even of reset or wake-up with halted 32 kHz

oscillator: from RSTIN falling edge or wake-up interrupt

it takes 560 ms at maximum for the start-up of the

32 kHz oscillator itself and the stabilization of the PLLs.

In the event of wake-up with running 32 kHz oscillator:

from wake-up interrupt it takes about 10 ms for the

stabilization of the PLLs.

After this start-up time, the microcontroller is supplied with

the system clock and - in case of a reset - the internally

stretched reset signal overlaps about 45

μ

s, to guarantee

a proper initialization of the microcontroller.

For further information refer to Chapter 15.

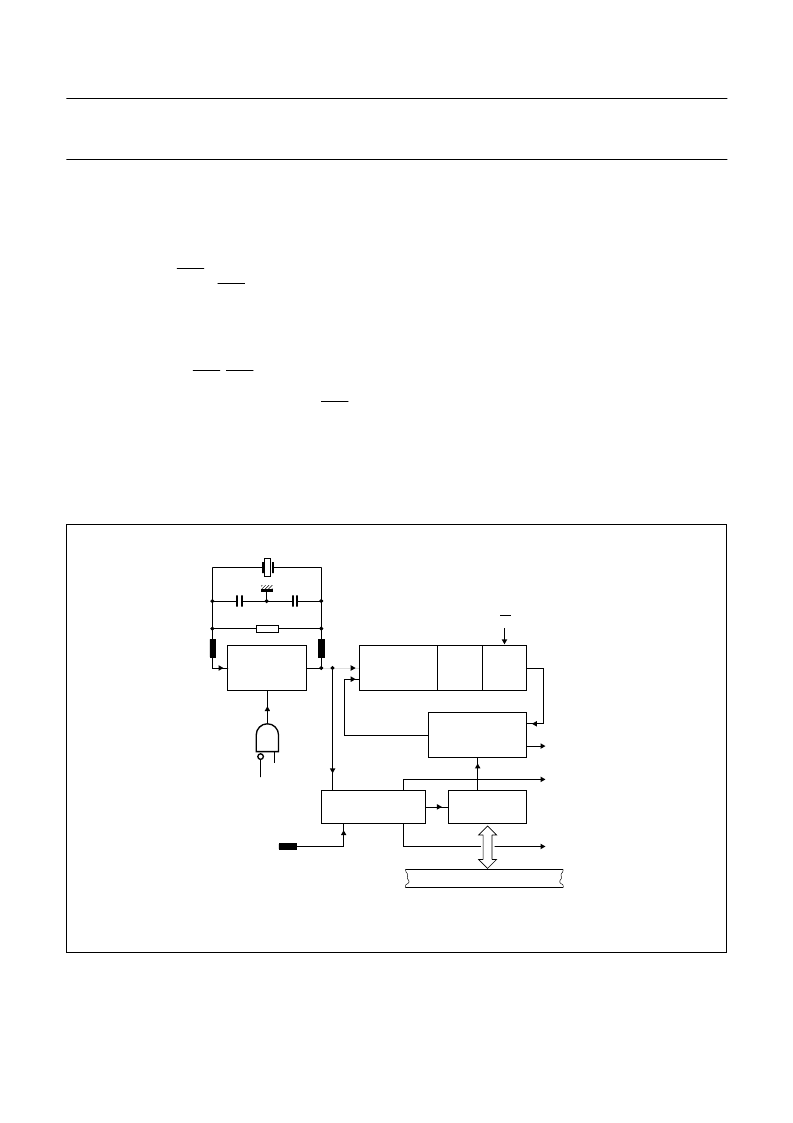

Fig.19 Block diagram PLL.

handbook, full pagewidth

MBH086

32 kHz

OCSILLATOR

PHASE

COMPARATOR

Rf

C1

C2

LOOP

FILTER

CCO

32.768 kHz

XTAL3

XTAL4

PROGRAMMABLE

DIVIDER

PLLCON

SECONDS TIMER

PD

PD

RUN32

RSTIN

INTERNAL BUS

'seconds'

interrupt

request

reset to

controller

system

clock

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P87C557E8 | 8 BIT MICROCONTROLLER |

| P8XC591 | HiRel FPGA, Low-Power 1.0?? CMOS Technology |

| P90CE201 | 16-bit microcontroller |

| P90CE201AEB | 16-bit microcontroller |

| P9217 | PbS photoconductive detector |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P8XC591 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Single-chip 8-bit microcontroller with CAN controller |

| P8XC592 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller with on-chip CAN |

| P8XCE598 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontroller with on-chip CAN |

| P8XCL580HFH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Low voltage 8-bit microcontrollers with UART, I2C-bus and ADC |

| P8XCL580HFT | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Low voltage 8-bit microcontrollers with UART, I2C-bus and ADC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。