- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376214 > MX98905B (Electronic Theatre Controls, Inc.) The MX98905 is designed for easy implementation of CSMA/CD local area networks, PDF資料下載

參數(shù)資料

| 型號: | MX98905B |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | The MX98905 is designed for easy implementation of CSMA/CD local area networks, |

| 中文描述: | 該MX98905是專為易于實現(xiàn)的多址/光盤局域網(wǎng), |

| 文件頁數(shù): | 27/86頁 |

| 文件大小: | 352K |

| 代理商: | MX98905B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁

27

P/N: PM0365

REV. 1.3, NOV 20 ,1995

MX98905B

signal Carrier Sense is asserted. It allows incoming

bits to be shifted into the shift register by the receive

clock provided by the SNC (Serial Network Converter).

The serial receive data is also routed to the CRC

generator/checker to detect CRC code. The receive

deserializer includes a synch detector that detects the

SFD (Start of Frame Delimiter) to establish where byte

boundaries within the serial bit stream are located, i.e.,

when a 1,1 bit sequence is detected, it begins to collect

data. After every eight receive clocks, the byte-wide

data is transferred to the 16-byte FIFO (two 8-byte

FIFOs) alternatively and the receive byte count is

incremented. The first six bytes after the SFD are

checked for valid comparison by the Address

Recognition Logic. If the address recognition Logic

does not recognize the packet, the FIFO is cleared.

21. ADDRESS RECOGNITION LOGIC

The address recognition logic compares the destina-

tion address field (first 6 bytes of the received packet)

with the physical address registers stored in the

address register array, one byte at a time, by the 8th

receive clock. If any one of the six bytes does not

match the pre-programmed physical address, the

protocol PLA rejects the packet. This means that the

packet does not belong to the node. All multicast

destination addresses are filtered using a hashing

technique by latching the 6 most significant bits of the

CRC generator. If the multicast address indexes a bit

that has been set in the filter bit array of the multicast

address register array, the packet is accepted.

Otherwise, it is rejected by the Protocol PLA. Each

destination address is also checked for all 1’s, which

is the reserved broadcast address.

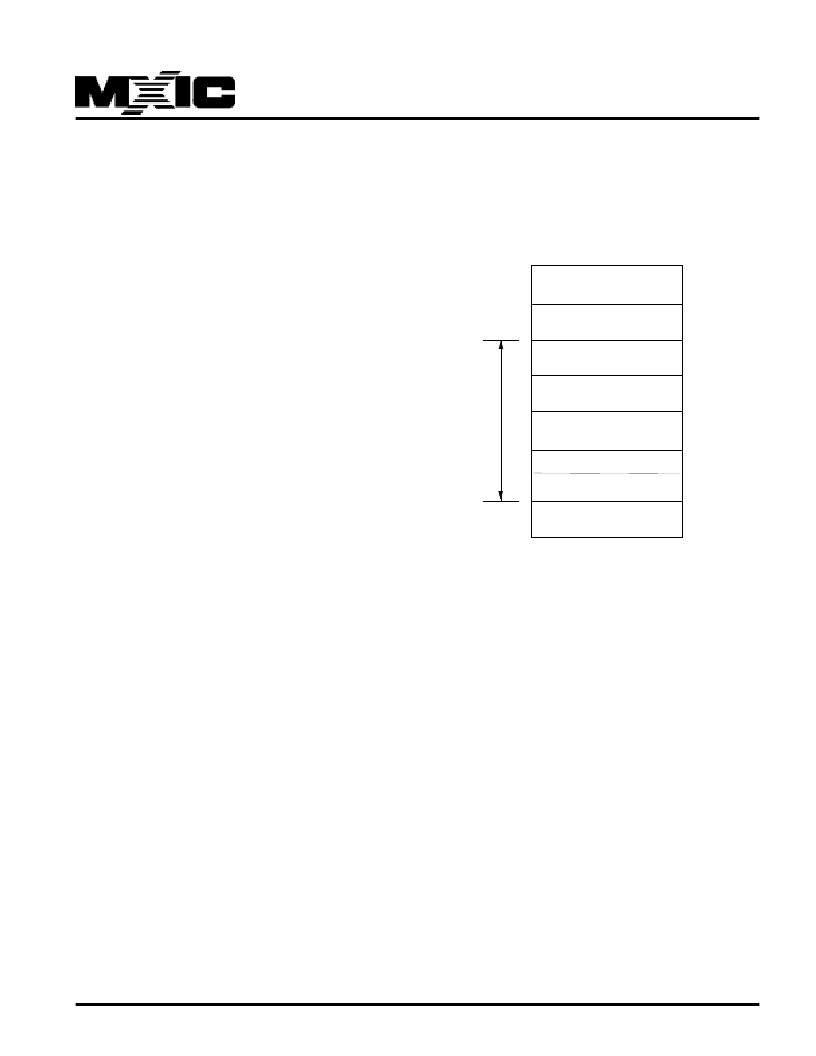

22. PACKET TRANSMISSION

A complete transmit packet consists of Preamble,

Synch, Data, and CRC fields. The data field is a

contiguous assembled packet of Destination Address.

Source Address, Length Field, and Data with the

format are shown below. During transmit, Page Start

Address Register (TPSR) and the Transmit Byte Count

Registers (TBCR0,1), control the DMA transfer. As a

transmit command is issued to ENC, the packet of data

in buffer memory pointed 0 by these registers will be

moved into the FIFO. The ENC will generate and

append the preamble, synch and CRC fields. In

addition, if transmitting data is smaller than 46 bytes,

the packet must be padded to a minimum size of 64

bytes. The programmer is responsible for adding and

stripping pad bytes.

GENERAL TRANSMIT PACKET FORMAT

PREAMBLE

SYNCH

DESTINATION ADDRESS

SOURCE ADDRESS

TYPE LENGTH

DATA

PAD (IF DATA < 46 BYTES)

CRC

62 BITS

2 BITS

6 BYTES

6 BYTES

2 BYTES

> 46 BYTES

4 BYTES

TX BYTE

COUNT

(TBCR 0, 1)

23. CONDITIONS REQUIRED TO BEGIN TRANS-

MISSION

To initiate transmission of a packet, the TPSR

(Transmit Page Start Register) and TBCR0, TBCR1

(Transmit Byte Count Registers) must be initialized

and the TXP bit in the Command Register must be set.

The ENC will start to prefetch transmit data from

memory, if no reception is currently receiving. Three

conditions must be met before transmission:

1. The Interframe Gap Timer has timed out the first

6.4

m

s of the Interframe Gap.

2. At least one byte has entered the FIFO, which

means that burst transfer has begun.

3. If collision occurs in the ENC, the backoff timer must

expire before retransmit.

If carrier sense is asserted before a byte has been

loaded into the FIFO, the ENC will become a receiver.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MX98905B | IEEE 802.3, 10BASE5, 10BASE2 Controller and Integrated Bus Interface(IEEE 802.3, 10BASE5, 10BASE2控制器和集成總線接口) |

| MX98905BFC | The MX98905 is designed for easy implementation of CSMA/CD local area networks, |

| MXA2312A | Low Cost, +2,-2 g Dual Axis Accelerometer with Analog Outputs |

| MXA2500K | Ultra Low Cost, 【1.0 g Dual Axis Accelerometer with Absolute Outputs |

| MXA2500KV | Ultra Low Cost, 【1.0 g Dual Axis Accelerometer with Absolute Outputs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MX98905BFC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:The MX98905 is designed for easy implementation of CSMA/CD local area networks, |

| MX98L715BEC | 制造商:MCNIX 制造商全稱:Macronix International 功能描述:3.3V SINGLE CHIP FAST ETHERNET NIC CONTROLLER |

| MX-9C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MX |

| MX-9G | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MX |

| MX9G100B | 制造商:Panasonic Industrial Company 功能描述:90x90 gearhead for 40W motor,100:1 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。