- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359235 > MT90823AP (ZARLINK SEMICONDUCTOR INC) 3V Large Digital Switch PDF資料下載

參數(shù)資料

| 型號: | MT90823AP |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 路由/交換 |

| 英文描述: | 3V Large Digital Switch |

| 中文描述: | TELECOM, DIGITAL TIME SWITCH, PQCC84 |

| 封裝: | PLASTIC, MS-018AF, LCC-84 |

| 文件頁數(shù): | 7/46頁 |

| 文件大?。?/td> | 663K |

| 代理商: | MT90823AP |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

MT90823

Data Sheet

7

Zarlink Semiconductor Inc.

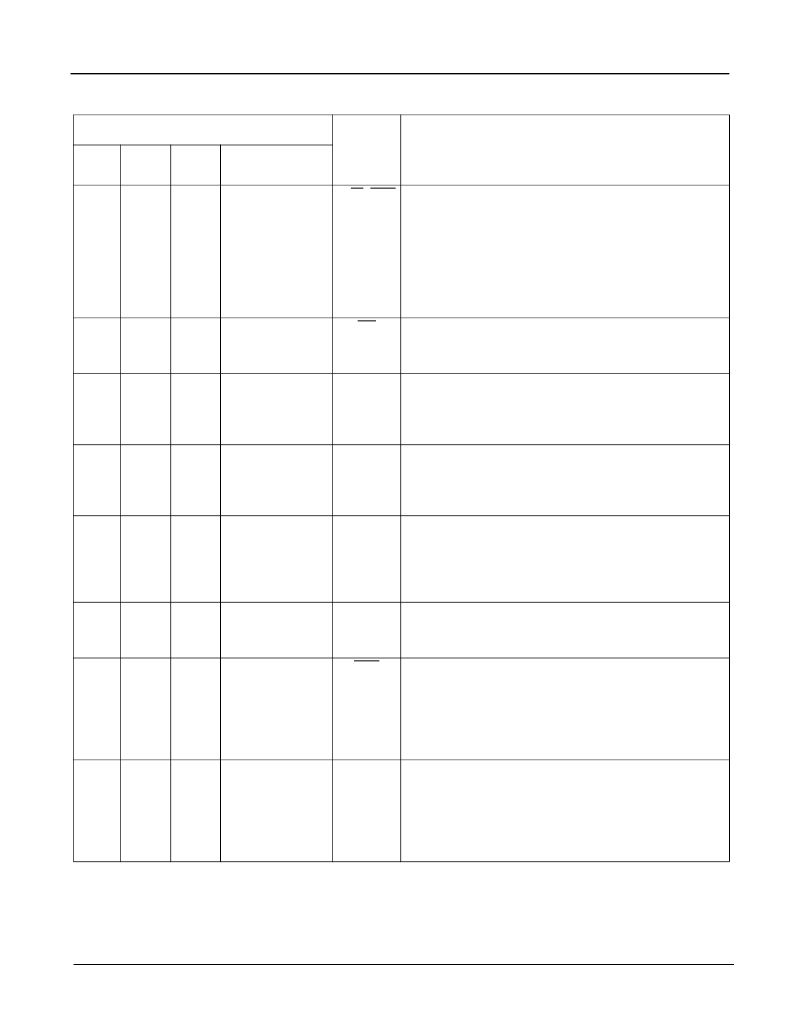

50

23

20

M10

R/W / WR

Read/Write / Write (5 V Tolerant Input):

In the cases

of Motorola non-multiplexed and multiplexed bus

operations, this input is R/W. This input controls the

direction of the data bus lines (AD0 - AD7, D8-D15)

during a microprocessor access.

For multiplexed bus operation, this input is WR. This

active low input is used with RD to control the data bus

(AD0 - 7) lines as inputs.

51

24

21

N12

CS

Chip Select (5 V Tolerant Input):

Active low input

used by a microprocessor to activate the

microprocessor port of MT90823.

52

25

22

M11

AS/ALE

Address Strobe or Latch Enable (5 V Tolerant

Input):

This input is used if multiplexed bus operation

is selected via the IM input pin. For Motorola non-

multiplexed bus operation, connect this pin to ground.

53

26

23

N13

IM

CPU Interface Mode (5 V Tolerant Input):

When IM is

high, the microprocessor port is in the multiplexed

mode. When IM is low, the microprocessor port is in

non-multiplexed mode.

55 -

62

32-39

29 -

36

L12,L13,K12,

K13,J12,J13,

H12,H13

AD0 - 7

Address/Data Bus 0 to 7 (5 V Tolerant I/O):

These

pins are the eight least significant data bits of the

microprocessor port. In multiplexed mode, these pins

are also the input address bits of the microprocessor

port.

65 -

72

42-49

39 -

46

G12,G13,F12,

F13,E12,E13,

D12,D13

D8 - 15

Data Bus 8-15 (5 V Tolerant I/O):

These pins are the

eight most significant data bits of the microprocessor

port.

73

50

47

C12

DTA

Data Transfer Acknowledgement (5 V tolerant

Three-state Output):

Indicates that a data bus transfer

is complete. When the bus cycle ends, this pin drives

HIGH and then tri-states, allowing for faster bus cycles

with a weaker pull-up resistor. A pull-up resistor is

required to hold a HIGH level when the pin is tri-stated.

74

55

48

C13

CSTo

Control Output (5 V Tolerant Output).

This is a

4.096, 8.192 or 16.384 Mb/s output containing 512,

1024 or 2048 bits per frame respectively. The level of

each bit is determined by the CSTo bit in the

connection memory. See External Drive Control

Section.

Pin Description (continued)

Pin #

Name

Description

84

PLCC

100

MQFP

100

LQFP

120

BGA

相關PDF資料 |

PDF描述 |

|---|---|

| MT90826 | Quad Digital Switch |

| MT90826AG | Quad Digital Switch |

| MT90826AL | Quad Digital Switch |

| MT90826AL1 | Quad Digital Switch |

| MT90826AV | Quad Digital Switch |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MT90823AP1 | 制造商:Microsemi Corporation 功能描述:LOW VOL LARGE DIGITAL SWCH |

| MT90826 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Quad Digital Switch |

| MT90826AG | 制造商:Zarlink Semiconductor Inc 功能描述:SWIT FABRIC 4K X 4K/2K X 2K/1K X 1K 3.3V 160BGA - Trays |

| MT90826AG2 | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 4K X 4K/2K X 2K/1K X 1K 3.3V 160BGA - Trays 制造商:Zarlink Semiconductor Inc 功能描述:SWIT FABRIC 4K X 4K/2K X 2K/1K X 1K 3.3V 160BGA - Trays |

| MT90826AL | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 4K X 4K/2K X 2K/1K X 1K 3.3V 160MQFP - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復。