- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69040 > MSM9225BGA-2K (OKI ELECTRIC INDUSTRY CO LTD) 2 CHANNEL(S), 1M bps, LOCAL AREA NETWORK CONTROLLER, PQFP44 PDF資料下載

參數(shù)資料

| 型號(hào): | MSM9225BGA-2K |

| 廠商: | OKI ELECTRIC INDUSTRY CO LTD |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, LOCAL AREA NETWORK CONTROLLER, PQFP44 |

| 封裝: | PLASTIC, QFP-44 |

| 文件頁數(shù): | 10/95頁 |

| 文件大小: | 567K |

| 代理商: | MSM9225BGA-2K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁

MSM9225B User’s Manual

Chapter 2 Register Descriptions

2 – 5

(1) Automatic transmission: ARES

If the automatic transmission of the data frame is used for remote frame reception, set this bit to “1”.

At reset, the ARES bit is set to “0”. The ARES bit is invalid if the message is specified as a group

message.

Notes on Automatic Transmission

Following shows how the transmission is carried out for the messages for which ARES is set to “1” when

a remote frame is received.

The MSM9225B detects the transmission priority of all the messages for which the TRQ (transmission

request) bit is set to “1”, then transmits the messages in sequence from the one with the highest priority.

Note, therefore, that messages for which automatic transmission is set will not always be transmitted

immediately after remote frame reception if there are any other messages to be transmitted.

Also in cases where there are some messages for which TRQ is set to “1”, whereas the TIRS bit of CANC

is not set to “1” because it is not yet desired to transmit them, those messages for which TRQ bit is set to

“1” will be transmitted.

(2) Frame type setting: FRM

This flag sets the frame type of the message to be transmitted/received. A message of a frame type other

than the specified frame type cannot be transmitted/received.

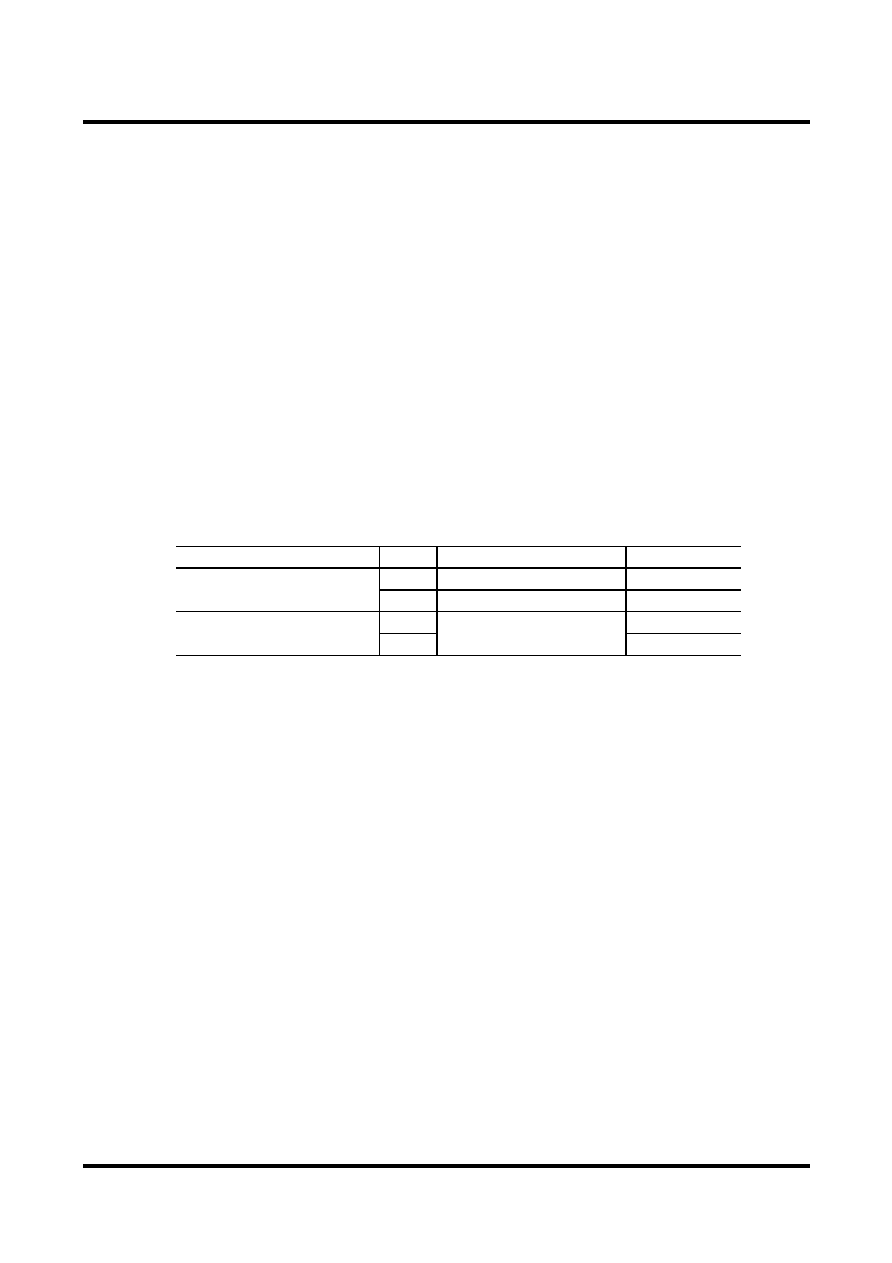

Table 2-2 shows the relationship between setting and frame type.

At reset, the FRM bit is set to “0”.

Table 2-2 Frame Types

Specified as group message

FRM

Transmission frame

Receive frame

0

Data frame

Remote frame

No

1

Remote frame

Data frame

0

Data frame

Yes

1

Transmission not activated

Remote frame

(3) Transmission completion interrupt enable: EIT

This is a flag to enable setting (“1”) the transmission interrupt request flag (ITF) when transmission

completes.

Set this flag from the microcontroller.

The EIT bit is valid when the EINTT bit of the CANI register is “1”. (See Section 2.4.2.)

At reset, the EIT bit is set to “0”.

(4) Receive completion interrupt enable: EIR

This is a flag to enable setting (“1”) the receive interrupt request flag (IRF) when receiving completes.

Set this flag from the microcontroller.

The EIR bit is valid when the EINTR bit of the CANI register is “1”. (See Section 2.4.2.)

At reset, the EIR bit is set to “0”.

(5) Receive status: RCS

When receiving completes, the RCS bit becomes “1”. Write “0” to the RCS bit before the micro-controller

reads receive data. When receiving the remote frame, the RCS bit becomes “1” just after the reception.

When receiving the data frame, it becomes “1” after receive data is written to the message box.

At reset, the RCS bit is set to “0”.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSP430A003IPW | 16-BIT, FLASH, 8 MHz, RISC MICROCONTROLLER, PDSO20 |

| MSP430A004IPWR | 16-BIT, 8 MHz, RISC MICROCONTROLLER, PDSO20 |

| MSP430A005IPWR | 16-BIT, 8 MHz, RISC MICROCONTROLLER, PDSO28 |

| MSP430A004IPW | 16-BIT, 8 MHz, RISC MICROCONTROLLER, PDSO20 |

| MSP430A019IRHBR | 16-BIT, FLASH, 8 MHz, RISC MICROCONTROLLER, PQCC64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSM9225BGAZ020 | 制造商:ROHM Semiconductor 功能描述: |

| MSM9225BGAZ0VL | 制造商:ROHM Semiconductor 功能描述: |

| MSM9405 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:IrDA Communication Controller |

| MSM9552 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:LSI for FM Multiplex Data Demodulation |

| MSM9552GS-2K | 制造商:ROHM Semiconductor 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。