- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45388 > MSC8254TVT800B (FREESCALE SEMICONDUCTOR INC) 0-BIT, OTHER DSP, PBGA783 PDF資料下載

參數(shù)資料

| 型號: | MSC8254TVT800B |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 0-BIT, OTHER DSP, PBGA783 |

| 封裝: | 29 X 29 MM, LEAD FREE, PLASTIC, FCBGA-783 |

| 文件頁數(shù): | 48/68頁 |

| 文件大?。?/td> | 909K |

| 代理商: | MSC8254TVT800B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁當(dāng)前第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

MSC8254 Quad-Core Digital Signal Processor Data Sheet, Rev. 4

Freescale Semiconductor

52

2.6.7

Asynchronous Signal Timing

Table 35 lists the asynchronous signal timing specifications.

The following interfaces use the specified asynchronous signals:

GPIO. Signals GPIO[31–0], when used as GPIO signals, that is, when the alternate multiplexed special functions are

not selected.

Note:

When used as a general purpose input (GPI), the input signal should be driven until it is acknowledged by the

MSC8254 device, that is, when the expected input value is read from the GPIO data register.

EE port. Signals EE0, EE1.

Boot function. Signal STOP_BS.

I

2C interface. Signals I2C_SCL and I2C_SDA.

Interrupt inputs. Signals IRQ[15–0] and NMI.

Interrupt outputs. Signals INT_OUT and NMI_OUT (minimum pulse width is 32 ns).

2.6.8

JTAG Signals

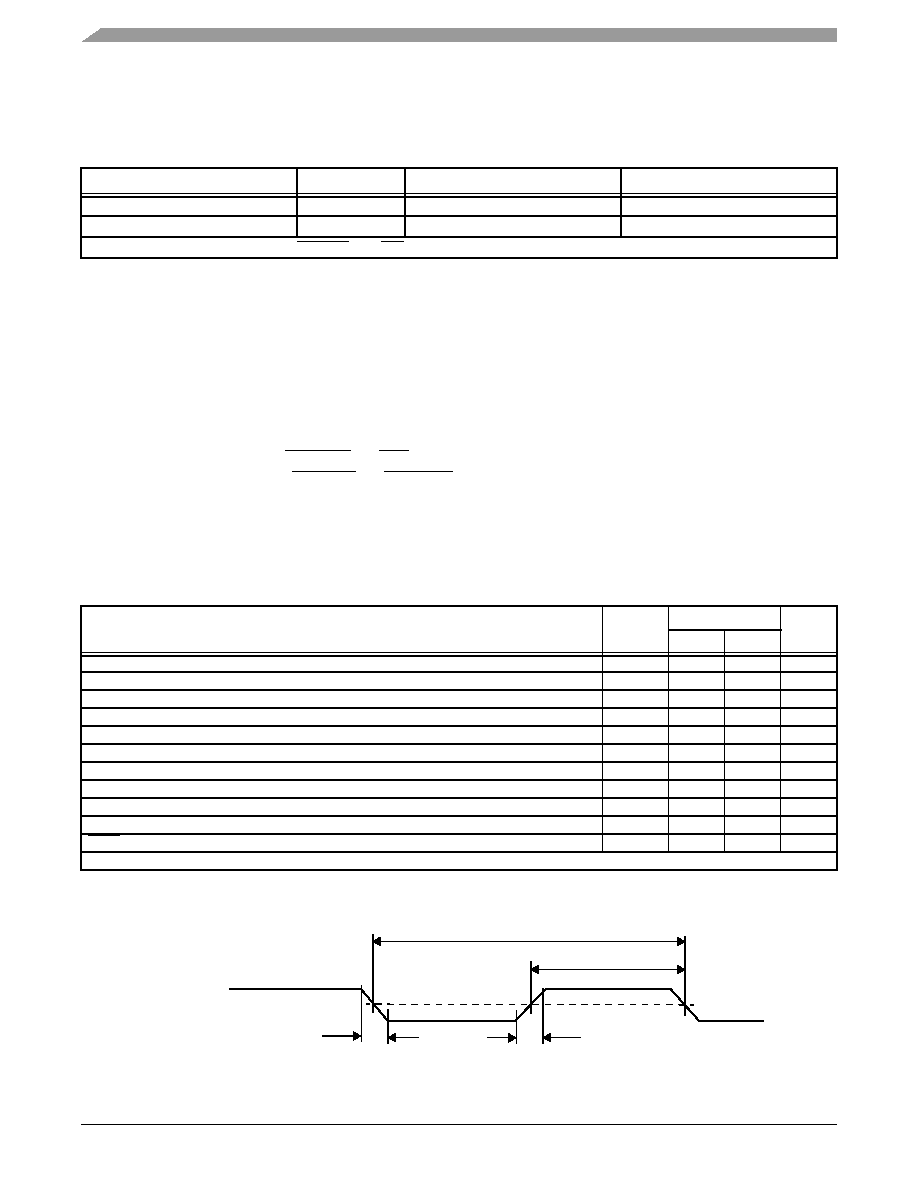

Figure 29 shows the test clock input timing diagram

Table 37. Signal Timing

Characteristics

Symbol

Type

Min

Input

tIN

Asynchronous

One CLKIN cycle

Output

tOUT

Asynchronous

Application dependent

Note:

Input value relevant for EE0, IRQ[15–0], and NMI only.

Table 38. JTAG Timing

Characteristics

Symbol

All frequencies

Unit

Min

Max

TCK cycle time

tTCKX

36.0

—

ns

TCK clock high phase measured at VM = VDDIO/2

tTCKH

15.0

—

ns

Boundary scan input data setup time

tBSVKH

0.0

—

ns

Boundary scan input data hold time

tBSXKH

15.0

—

ns

TCK fall to output data valid

tTCKHOV

—

20.0

ns

TCK fall to output high impedance

tTCKHOZ

—

24.0

ns

TMS, TDI data setup time

tTDIVKH

0.0

—

ns

TMS, TDI data hold time

tTDIXKH

5.0

—

ns

TCK fall to TDO data valid

tTDOHOV

—

10.0

ns

TCK fall to TDO high impedance

tTDOHOZ

—

12.0

ns

TRST assert time

tTRST

100.0

—

ns

Note:

All timings apply to OnCE module data transfers as well as any other transfers via the JTAG port.

Figure 29. Test Clock Input Timing

TCK

(Input)

VM

tTCKX

tTCKH

tTCKR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSC8254SVT800B | 0-BIT, OTHER DSP, PBGA783 |

| MSC8254TVT1000B | 0-BIT, OTHER DSP, PBGA783 |

| MSC8256SVT800B | 0-BIT, OTHER DSP, PBGA783 |

| MSC8256TVT800B | 0-BIT, OTHER DSP, PBGA783 |

| MSC8256SVT1000B | 0-BIT, OTHER DSP, PBGA783 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSC8256 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Six-Core Digital Signal Processor |

| MSC8256_11 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Six-Core Digital Signal Processor |

| MSC8256ETAG1000B | 制造商:Freescale Semiconductor 功能描述:DSP,STARCORE, 6-CORE - Bulk |

| MSC8256SAG1000B | 制造商:Freescale Semiconductor 功能描述:DSP,STARCORE,6-CORE R2.1 - Bulk |

| MSC8256SVT1000B | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC DSPStarcore6-core R2.1 RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。