- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25632 > MPC9991FA (MOTOROLA INC) PLL BASED CLOCK DRIVER, 13 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 PDF資料下載

參數(shù)資料

| 型號: | MPC9991FA |

| 廠商: | MOTOROLA INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | PLL BASED CLOCK DRIVER, 13 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| 封裝: | PLASTIC, LQFP-52 |

| 文件頁數(shù): | 5/11頁 |

| 文件大?。?/td> | 144K |

| 代理商: | MPC9991FA |

MPC9991

MOTOROLA ADVANCED CLOCK DRIVERS DEVICE DATA

290

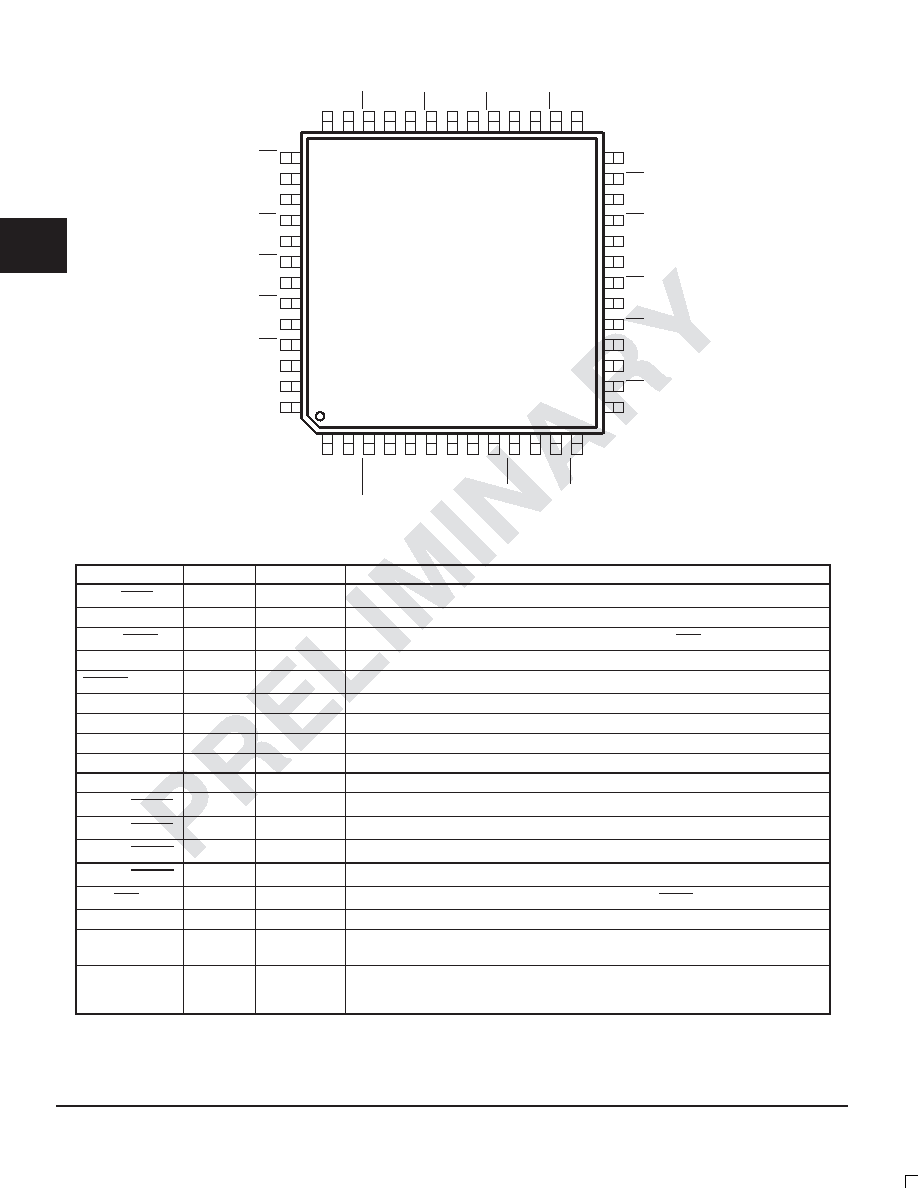

Figure 2. MPC9991 52–Lead Package Pinout (Top View)

QB3

VCC

QA0

QA1

QA2

QA3

SYNC_SEL

VCO_SEL

QC1

QCO

QC0

VCC

QD1

QD0

VCC

QFB

VCC_PLL

FSEL0

QB2

FSEL1

QB1

FSEL2

QB0

VCC

QC2

FSEL3

VEE

MR

PLL_EN

REF_SEL

FSEL_FB2

FSEL_FB1

FSEL_FB0

TCLK

ECLK

VCC

FB_IN

40

41

42

43

44

45

46

47

48

49

50

51

52

25

24

23

22

21

20

19

18

17

16

15

14

12 34 56 78 9 10 11 12 13

39 38 37 36 35 34 33 32 31 30 29 28 27

26

MPC9991

Table 1: PIN CONFIGURATION

Pin

I/O

Type

Function

ECLK, ECLK

Input

PECL/ECL

Differential reference clock signal input

TCLK

Input

PECL/ECL

Single-ended test clock input

FB_IN, FB_IN

Input

PECL/ECL

Differential PLL feedback clock signal input, connect to QFB, QFB

VCO_SEL

Input

PECL/ECL

VCO operating frequency select

PLL_EN

Input

PECL/ECL

PLL Enable/Bypass mode select

REF_SEL

Input

PECL/ECL

PLL reference signal input select

MR

Input

PECL/ECL

Device reset

FSEL[3:0]

Input

PECL/ECL

Output frequency divider select

FSEL_FB[2:0]

Input

PECL/ECL

Frequency divider select for the QFB output

SYNC_SEL

Input

PECL/ECL

QD output mode select

QA[0-3], QA[0-3]

Output

PECL/ECL

Differential clock outputs (bank A)

QB[0-3], QB[0-3]

Output

PECL/ECL

Differential clock outputs (bank B)

QC[0-2], QC[0-2]

Output

PECL/ECL

Differential clock outputs (bank C)

QD[0-1], QD[0-1]

Output

PECL/ECL

Differential clock/SYNC signal outputs (bank D)

QFB, QFB

Output

PECL/ECL

Differential PLL feedback clock output (connect to FB_IN, FB_IN)

VEEa

Supply

VEE

Negative power supply

VCC

Supply

VCC

Positive power supply. All VCC pins must be connected to the positive power supply for

correct DC and AC operation

VCC_PLL

Supply

VCC

PLL positive power supply (analog power supply). It is recommended to use an external

RC filter for the analog power supply pin VCC_PLL. Please see applications section for

details

a.

In ECL mode (negative power supply mode), VEE is -3.3V and VCC is connected to GND (0V).

In PECL mode (positive power supply mode), VEE is connected to GND (0V) and VCC is +3.3V.

In both modes, the input and output levels are referenced to the most positive supply (VCC).

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MQ80C154-16P883R | 8-BIT, 16 MHz, MICROCONTROLLER, CQFP44 |

| 952100202 | 8-BIT, 30 MHz, MICROCONTROLLER, CQCC44 |

| MD80C52EXXX-30SBD | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, CDIP40 |

| MQ80C32E-30SCR | 8-BIT, 30 MHz, MICROCONTROLLER, CQFP44 |

| MC80C32E-36SB | 8-BIT, 36 MHz, MICROCONTROLLER, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC9992 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:3.3 DIFFRERENTIAL ECL/PECL PLL CLOCK GENERATOR |

| MPC9992AC | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| MPC9992ACR2 | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| MPC9992FA | 功能描述:鎖相環(huán) - PLL 2.5 3.3V 400MHz Clock Generator RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| MPC9992FAR2 | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 32-Pin LQFP T/R |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。