- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄45337 > MPC106ARX66CG PCI BUS CONTROLLER, CBGA304 PDF資料下載

參數(shù)資料

| 型號(hào): | MPC106ARX66CG |

| 元件分類(lèi): | 總線(xiàn)控制器 |

| 英文描述: | PCI BUS CONTROLLER, CBGA304 |

| 封裝: | 21 X 25 MM, 3.16 MM HEIGHT, 1.27 MM PITCH, CERAMIC, BGA-304 |

| 文件頁(yè)數(shù): | 7/32頁(yè) |

| 文件大小: | 451K |

| 代理商: | MPC106ARX66CG |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

Tsi106 PowerPC Host Bridge Hardware Specifications Manual

15

80C1000_MA002_02

Electrical and Thermal Characteristics

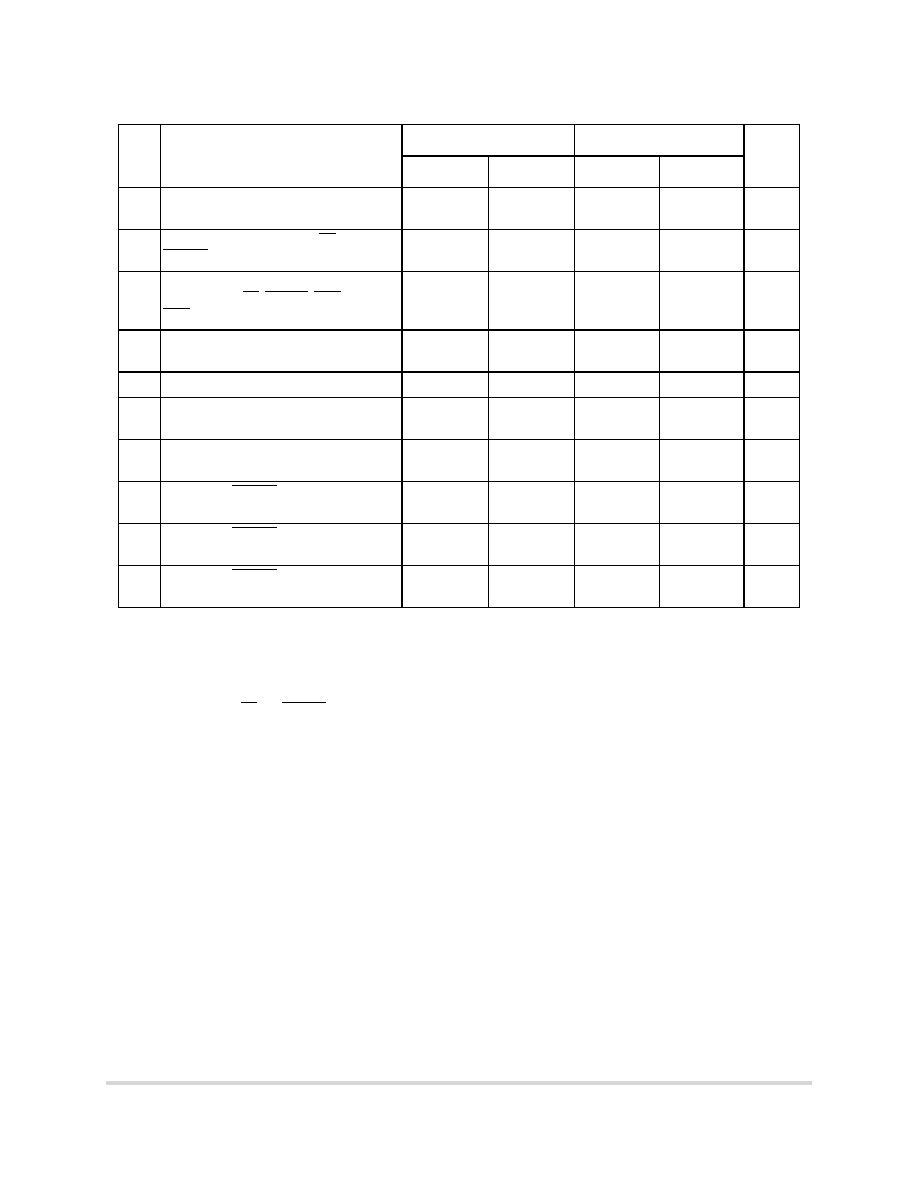

Table 8. Output AC Timing Specifications

Num

Characteristic

66 MHz

83.3 MHz

Notes

Min

Max

Min

Max

12

SYSCLK to output driven (output enable

time)

2.0

—

2.0

—

1

13a

SYSCLK to output valid for TS and

ARTRY

—

7.0

—

6.0

2, 3, 4

13b

SYSCLK to output valid for all non-PCI

signals except TS, ARTRY, RAS[0–7],

CAS[0–7], and DWE[0-2]

—

7.0

—

6.0

2, 3, 5

14a

SYSCLK to output valid (for RAS[0–7]

and CAS[0–7])

—

7.0

—

6.0

2, 3

14b

SYSCLK to output valid for PCI signals

—

11.0

—

11.0

3, 6

15a

SYSCLK to output invalid for all non-PCI

signals (output hold)

1.0

—

1.0

—

7, 10

15b

SYSCLK to output invalid for PCI signals

(output hold)

1.0

—

1.0

—

7

18

SYSCLK to ARTRY high impedance

before precharge (output hold)

—

8.0

—

8.0

1

19

SYSCLK to ARTRY precharge enable

(0.4 *

tsysclk) + 2.0

—

(0.4 x

tsysclk) + 2.0

—8, 1

21

SYSCLK to ARTRY high impedance after

precharge

—

(1.5 *

tsysclk) + 8.0

—

(1.5 x

tsysclk) + 8.0

8, 1

Notes:

1 These values are guaranteed by design and are not tested.

2 Output specifications are measured from 1.4 V on the rising edge of the appropriate clock to the TTL level (0.8 V or 2.0 V)

of the signal in question. Both input and output timings are measured at the pin (see Figure 5).

3 The maximum timing specification assumes CL = 50 pF.

4 The shared outputs TS and ARTRY require pull-up resistors to hold them negated when there is no bus master driving them.

5 When the Tsi106 is configured for asynchronous L2 cache SRAMs, the DWE[0–2] signals have a maximum SYSCLK to

output valid time of (0.5 x tPROC) + 8.0 ns (where tPROC is the 60x bus clock cycle time).

6 PCI 3.3 V signaling environment signals are measured from 1.65 V (Vdd ÷ 2) on the rising edge of SYSCLK to V

OH =3.0 V

or VOL =0.3 V.

7 The minimum timing specification assumes CL = 0 pF.

8 t

sysclk is the period of the external bus clock (SYSCLK) in nanoseconds (ns). When the unit is given as tsysclk the numbers

given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in nanoseconds) of the

parameter in question.

9 PCI devices which require more than the PCI-specified hold time of T

h = 0ns or systems where clock skew approaches the

PCI-specified allowance of 2ns may not work with the Tsi106.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC5200BV400 | 400 MHz, MICROPROCESSOR, PBGA272 |

| MPC5200CBV266R2 | 266 MHz, MICROPROCESSOR, PBGA272 |

| MPC5200CBV266BR2 | 266 MHz, MICROPROCESSOR, PBGA272 |

| MPC5200BV400B | 400 MHz, MICROPROCESSOR, PBGA272 |

| MPC5200CBV400B | 400 MHz, MICROPROCESSOR, PBGA272 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC106ARX66DE | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:PCI Bridge/Memory Controller |

| MPC106ARX66DG | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:PCI Bridge/Memory Controller |

| MPC106ARX66TE | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:PCI Bridge/Memory Controller |

| MPC106ARX66TG | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:PCI Bridge/Memory Controller |

| MPC106ARX83CE | 制造商:MOTOROLA 制造商全稱(chēng):Motorola, Inc 功能描述:PCI Bridge/Memory Controller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。