- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69034 > ML60851EGA (OKI ELECTRIC INDUSTRY CO LTD) UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 PDF資料下載

參數(shù)資料

| 型號: | ML60851EGA |

| 廠商: | OKI ELECTRIC INDUSTRY CO LTD |

| 元件分類: | 總線控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| 封裝: | 0.80 MM PITCH, PLASTIC, QFP-44 |

| 文件頁數(shù): | 70/88頁 |

| 文件大?。?/td> | 1137K |

| 代理商: | ML60851EGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁當前第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

Oki Semiconductor

ML60851E

70/84

(5) Transmit packet ready interrupts (EP1, EP2, EP3)

These interrupts are generated when it is possible for the local MCU to write the data packet to be sent to the

USB bus from the corresponding EP.

Operation

Source of operation

Description (conditions, responses, etc.)

Transmit packet ready

interrupt generation

ML60851E

(1) In the case of bulk transfer and interrupt transfer

When the respective EP has been set for transmission,

the transmit packet ready bit of the corresponding EP is

de-asserted when it is possible to write the transmit

data into the FIFO.

At this time, an interrupt is generated if the

corresponding EP transmit packet ready interrupt

enable bit (INTENBL) has been asserted.

For the second and subsequent packets, in addition to

this condition, before the interrupt is generated, it is

necessary for an ACK response to come from the host

for the packet that has just been sent.

End of transmit packet ready

interrupt

Local MCU (firmware)

(1) In the case of bulk transfer and interrupt transfer

After the one packet of the corresponding EP transmit

data has been written in EPnTXFIFO, write a “1” into

the corresponding transmit packet ready bit (PKTRDY

register). This puts the ML60851E in a state in which it

can transmit the data and the

INTR pin is de-asserted

at the same time.

When the number of bytes in the write data is less than

the maximum payload size of the endpoint, a short

packet can be transmitted by writing a “1” into the

transmit packet ready bit (PKTRDY register).

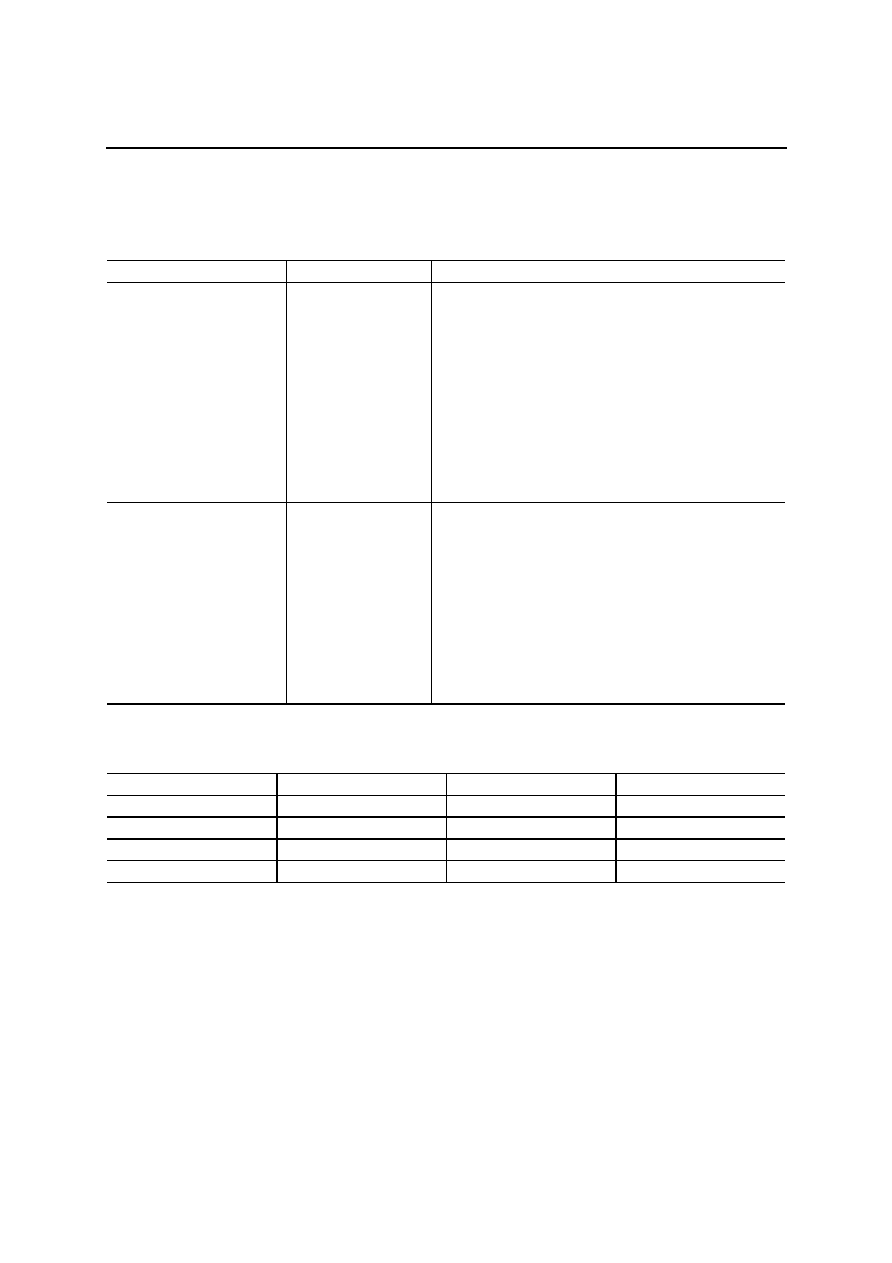

The following table outlines the relationship between ML60851E registers and packet ready interrupt generation

during a transmit (device to host communication) operation.

INTENBL(D1/D2/D7)*

EPnCON(D7)

I

Tx PKTRDY(D5/D6/D7)*

INTSTAT(D1/D2/D7)*

1

0

X

0

1

0

1

0

1

0

X

0

X This symbol means that it does not matter whether the value is ‘1’ or ‘0’

* Use the appropriate bit field corresponding to the endpoint being considered

I

EP3 is only capable of transmission and hence this register does not play a roll in interrupt generation of EP3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ML60851ETB | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| ML610Q346 | RISC MICROCONTROLLER, PQFP64 |

| ML610346 | RISC MICROCONTROLLER, PQFP64 |

| ML610Q347J-NNNTB | 8-BIT, FLASH, 4.2 MHz, RISC MICROCONTROLLER, PQFP64 |

| ML610347-XXXTB | 8-BIT, MROM, 4.2 MHz, RISC MICROCONTROLLER, PQFP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ML60851ETB | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:USB Device Controller |

| ML60852 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:USB Device Controller |

| ML60852A | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:USB Device Controller |

| ML60852ATBZ010 | 功能描述:USB 接口集成電路 12 Mbps; USB Device Controller RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| ML60852ATBZ03A | 制造商:ROHM Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。