- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69032 > MCM16Y1BGCFT16 (FREESCALE SEMICONDUCTOR INC) 16-BIT, MROM, MICROCONTROLLER, PQFP160 PDF資料下載

參數(shù)資料

| 型號: | MCM16Y1BGCFT16 |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 16-BIT, MROM, MICROCONTROLLER, PQFP160 |

| 封裝: | QFP-160 |

| 文件頁數(shù): | 10/138頁 |

| 文件大小: | 784K |

| 代理商: | MCM16Y1BGCFT16 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁

MC68HC16Y1

MOTOROLA

MC68HC16Y1TS/D

107

7.2.3 SPI Operation

The SPI operates in either master or slave mode. Master mode is used when the SPI originates data

transfers. Slave mode is used when an external device initiates serial transfers to the SPI. Switching

between the modes is controlled by MSTR in SPCR. Prior to entering either mode, appropriate MCCI

and SPI registers must be properly initialized.

In master mode, transmission parameters are set by writing to SPCR, the SPI is enabled by setting

SPE, then operation is initiated by writing data to SPDR. In slave mode, operation proceeds in response

to SS signal assertion by an external bus master. Slave operation is similar to that of master mode.

Normally, the SPI bus performs synchronous bidirectional transfers. The serial clock on the SPI bus

master supplies the clock signal (SCK) to time the transfer of data. Four possible combinations of clock

phase and polarity may be specified by means of the CPHA and CPOL bits in SPCR. Data can be trans-

ferred either LSB or MSB first, depending on the value of the LSBF bit in SPCR. The number of bits

transferred per command defaults to eight, but may be set to 16 bits by setting the field in SPCR.

When the SPI finishes a transmission, it sets the SPIF flag, clears SPE and stops. If the SPIE bit in

SPCR is set, an interrupt request is generated when SPIF is set.

Although the SPI inherently supports multimaster operation, no special arbitration mechanism is provid-

ed. A mode fault flag (MODF) indicates a request for SPI master arbitration — system software must

provide arbitration.

Typically, SPI bus outputs are not open-drain unless multiple SPI masters are in the system. If needed,

the WOMP bit in SPCR can be set to provide wired-OR open-drain outputs. An external pull-up resistor

should be used on each output line. WOMP affects all SPI pins regardless of whether they are assigned

to the SPI or used as general-purpose I/O.

7.3 Serial Communication Interface

There are two identical independent SCI systems, SCIA and SCIB, in the MCCI. Each is a full-duplex

universal asynchronous receiver transmitter (UART). Each SCI system is fully compatible with the SCI

systems found on other Motorola devices, such as the M68HC11 and M68HC05 Families. The following

discussions apply to both SCIA and SCIB — differences in register addresses and pin names are noted.

7.3.1 SCI Pins

Two unidirectional transmit data pins, TXDA and TXDB, and two unidirectional receive data pins, RXDA

and RXDB, are associated with each SCI. Each pin can be used by the associated SCI or for general-

purpose I/O.

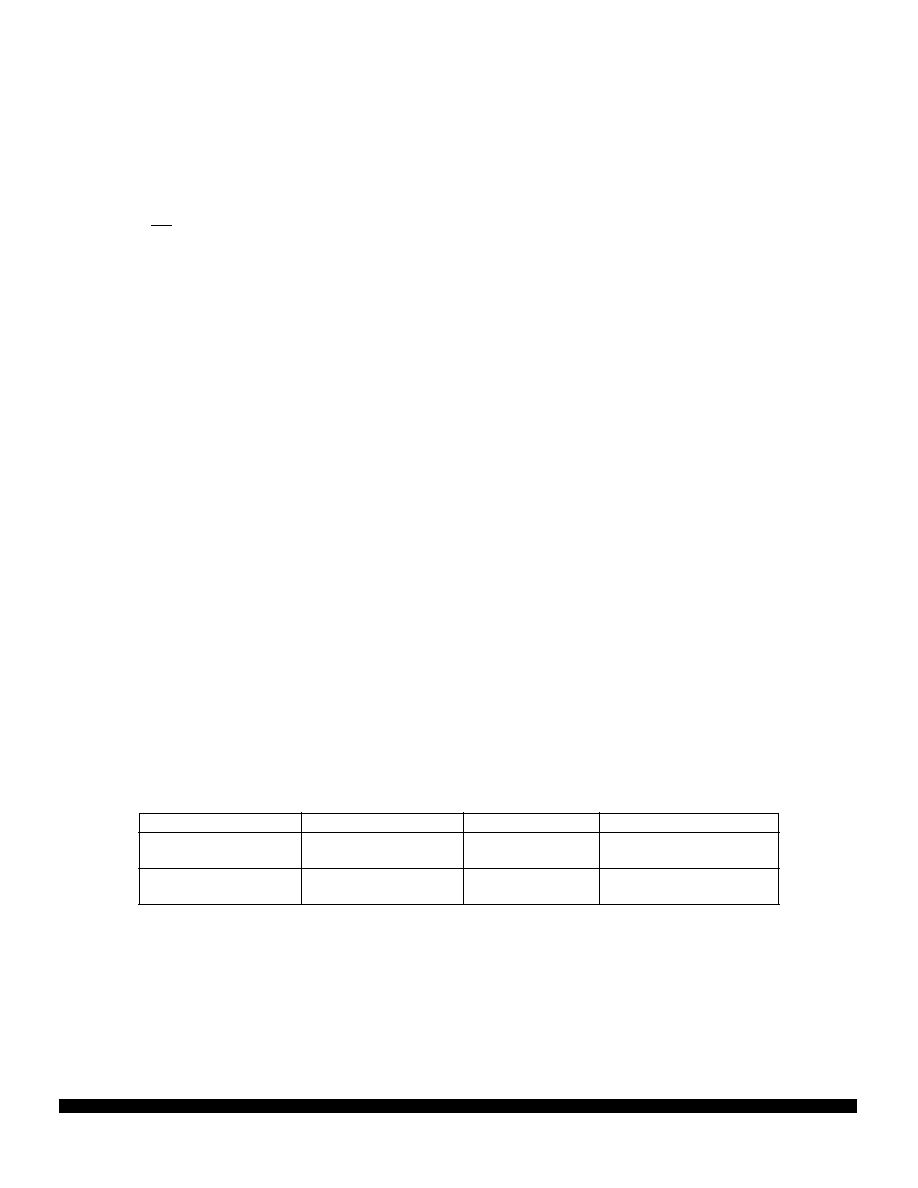

SCI pins and their functions are shown below.

7.3.2 SCI Registers

The SCI programming model includes the MCCI global and pin control registers, and eight SCI regis-

ters. Each of the two SCI units contains two SCI control registers, one status register, and one data reg-

ister.

All registers may be read or written at any time by the CPU. Rewriting the same value to any SCI register

does not disrupt operation; however, writing a different value into an SCI register when the SCI is run-

ning may disrupt operation. To change register values, the receiver and transmitter should be disabled

with the transmitter allowed to finish first. The status flags in register SCSR may be cleared at any time.

Pin Names

Mnemonics

Mode

Function

Receive Data

A and B

RXDA, RXDB

Receiver Disabled

Receiver Enabled

General-Purpose I/O

Serial Data Input to SCI

Transmit Data

A and B

TXDA, TXDB

Transmitter Disabled

Transmitter Enabled

General-Purpose I/O

Serial Data Output from SCI

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M68HC16Y1CFC | 16-BIT, MROM, MICROCONTROLLER, PQFP16 |

| MCV14AI/SL | 8-BIT, FLASH, 20 MHz, RISC MICROCONTROLLER, PDSO14 |

| MCV14ATI/SL | 8-BIT, FLASH, 20 MHz, RISC MICROCONTROLLER, PDSO14 |

| MCV14AI/P | 8-BIT, FLASH, 20 MHz, RISC MICROCONTROLLER, PDIP14 |

| MD8031AHB883B | 8-BIT, 12 MHz, MICROCONTROLLER, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCM16Z2BCFC16 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Symbols and Operators, CPU16 Register Mnemonics |

| MCM16Z2BCFC16B1 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Symbols and Operators, CPU16 Register Mnemonics |

| MCM16Z2BCFC20 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Symbols and Operators, CPU16 Register Mnemonics |

| MCM16Z2BCFC20B1 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:M68HC16Z Series users manual |

| MCM16Z2BCFC25 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:M68HC16Z Series users manual |

發(fā)布緊急采購,3分鐘左右您將得到回復。