參數資料

| 型號: | MAX3108EWA+T |

| 廠商: | Maxim Integrated Products |

| 文件頁數: | 44/56頁 |

| 文件大小: | 0K |

| 描述: | IC UART |

| 產品培訓模塊: | Obsolescence Mitigation Program |

| 標準包裝: | 2,500 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

SPI/I2C UART with 128-Word FIFOs in WLP

MAX3108

49

Maxim Integrated

I2C Interface

The MAX3108 contains an I2C-compatible interface for

data communication with a host processor (SCL and

SDA). The interface supports a clock frequency of up

to 1MHz. SCL and SDA require pullup resistors that are

connected to a positive supply.

START, STOP, and Repeated START Conditions

When writing to the MAX3108 using I2C, the master

sends a START condition (S) followed by the MAX3108

I2C address. After the address, the master sends

the register address of the register that is to be pro-

grammed. The master then ends communication by

issuing a STOP condition (P) to relinquish control of the

bus, or a repeated START condition (Sr) to communicate

to another I2C slave. See Figure 17.

Slave Address

The MAX3108 includes a configurable 7-bit I2C slave

address, allowing up to 16 MAX3108 devices to share

the same I2C bus. The address is defined by connect-

ing the MOSI/A1 and CS/A0 inputs to DGND, VL, SCL,

or SDA (Table 5). Set the R/W bit high to configure the

MAX3108 to read mode. Set the R/W bit low to config-

ure the MAX3108 to write mode. The address is the

first byte of information sent to the MAX3108 after the

START condition.

Bit Transfer

One data bit is transferred on the rising edge of each

SCL clock cycle. The data on SDA must remain stable

during the high period of the SCL clock pulse. Changes

in SDA while SCL is high and stable are considered

control signals (see the START, STOP, and Repeated

START Conditions section). Both SDA and SCL remain

high when the bus is not active.

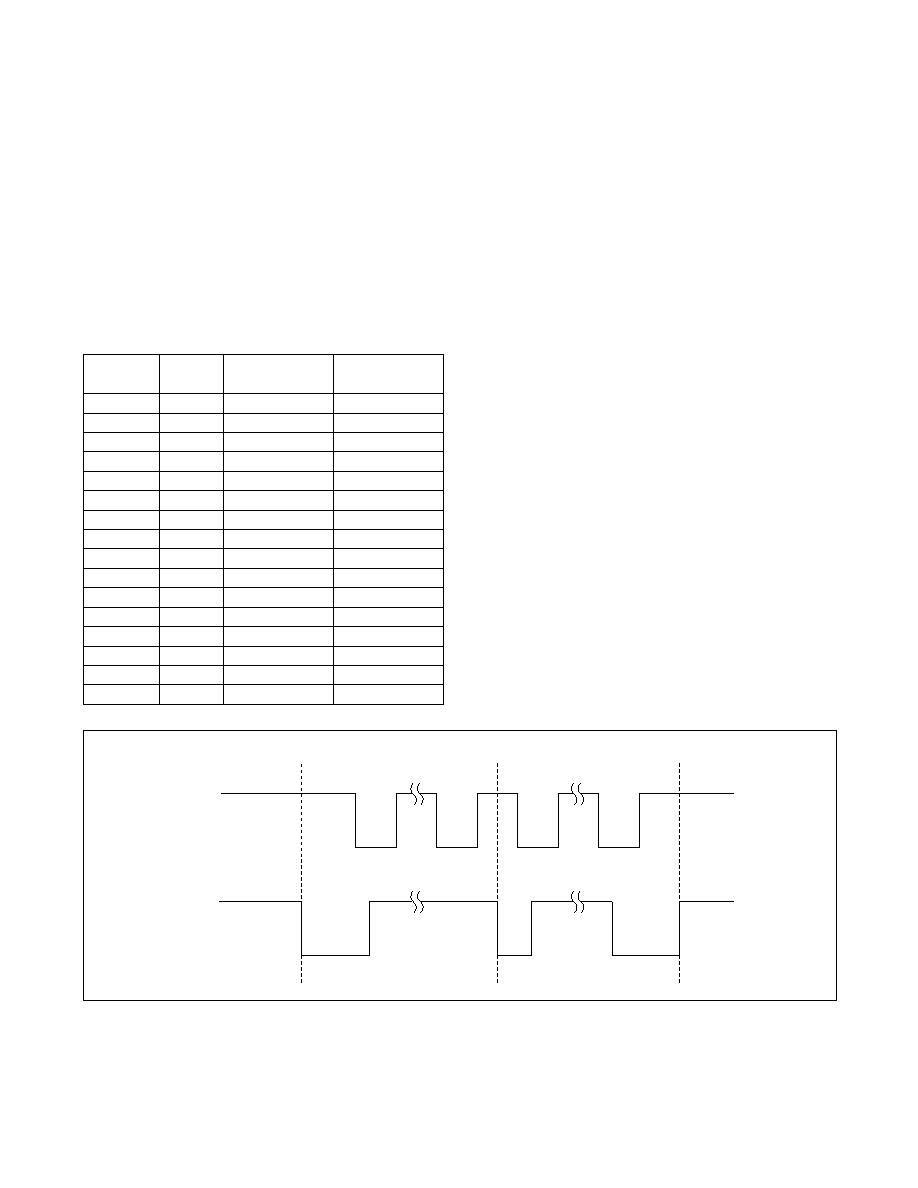

Figure 17. I2C START, STOP, and Repeated START Conditions

Table 5. I2C Address Map

SCL

SDA

SSrP

MOSI/A1

CS/A0

I2C WRITE

ADDRESS

I2C READ

ADDRESS

DGND

0xD8

0xD9

DGND

VL

0xC2

0xC3

DGND

SCL

0xC4

0xC5

DGND

SDA

0xC6

0xC7

VL

DGND

0xC8

0xC9

VL

0xCA

0xCB

VL

SCL

0xCC

0xCD

VL

SDA

0xCE

0xCF

SCL

DGND

0xD0

0xD1

SCL

VL

0xD2

0xD3

SCL

0xD4

0xD5

SCL

SDA

0xD6

0xD7

SDA

DGND

0xC0

0xC1

SDA

VL

0xDA

0xDB

SDA

SCL

0xDC

0xDD

SDA

0xDE

0xDF

相關PDF資料 |

PDF描述 |

|---|---|

| MAX3109ETJ+ | SEMICONDUCTOR OTHER |

| MAX310CPE | IC VIDEO MULTIPLEXER 8X1 16DIP |

| MAX3110EENI+G36 | IC UART SPI COMPAT 28-DIP |

| MAX3120CUA+ | IC TXRX INFRARED IRDA 8-UMAX |

| MAX3120EUA | IC TXRX 3V IRDA IR 3V 8-UMAX |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MAX3109ETJ+ | 功能描述:UART 接口集成電路 Dual Serial UART with 128-Word FIFOs RoHS:否 制造商:Texas Instruments 通道數量:2 數據速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| MAX3109ETJ+T | 功能描述:UART 接口集成電路 Dual Serial UART with 128-Word FIFOs RoHS:否 制造商:Texas Instruments 通道數量:2 數據速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| MAX310C/D | 功能描述:多路器開關 IC RoHS:否 制造商:Texas Instruments 通道數量:1 開關數量:4 開啟電阻(最大值):7 Ohms 開啟時間(最大值): 關閉時間(最大值): 傳播延遲時間:0.25 ns 工作電源電壓:2.3 V to 3.6 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:UQFN-16 |

| MAX310CPE | 功能描述:多路器開關 IC RoHS:否 制造商:Texas Instruments 通道數量:1 開關數量:4 開啟電阻(最大值):7 Ohms 開啟時間(最大值): 關閉時間(最大值): 傳播延遲時間:0.25 ns 工作電源電壓:2.3 V to 3.6 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:UQFN-16 |

| MAX310CPE+ | 功能描述:多路器開關 IC 8:1 Unbuffered RF Video MUX RoHS:否 制造商:Texas Instruments 通道數量:1 開關數量:4 開啟電阻(最大值):7 Ohms 開啟時間(最大值): 關閉時間(最大值): 傳播延遲時間:0.25 ns 工作電源電壓:2.3 V to 3.6 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:UQFN-16 |

發(fā)布緊急采購,3分鐘左右您將得到回復。