- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370825 > M2V28D20ATP-75 (Mitsubishi Electric Corporation) 128M Double Data Rate Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號(hào): | M2V28D20ATP-75 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 128M Double Data Rate Synchronous DRAM |

| 中文描述: | 128M的雙數(shù)據(jù)速率同步DRAM |

| 文件頁(yè)數(shù): | 4/36頁(yè) |

| 文件大小: | 1216K |

| 代理商: | M2V28D20ATP-75 |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

4

MITSUBISHI ELECTRIC

Jun,'00

Preliminary

MITSUBISHI LSIs

DDR SDRAM (Rev.0.1)

M2S28D20/ 30/ 40ATP

128M Double Data Rate Synchronous DRAM

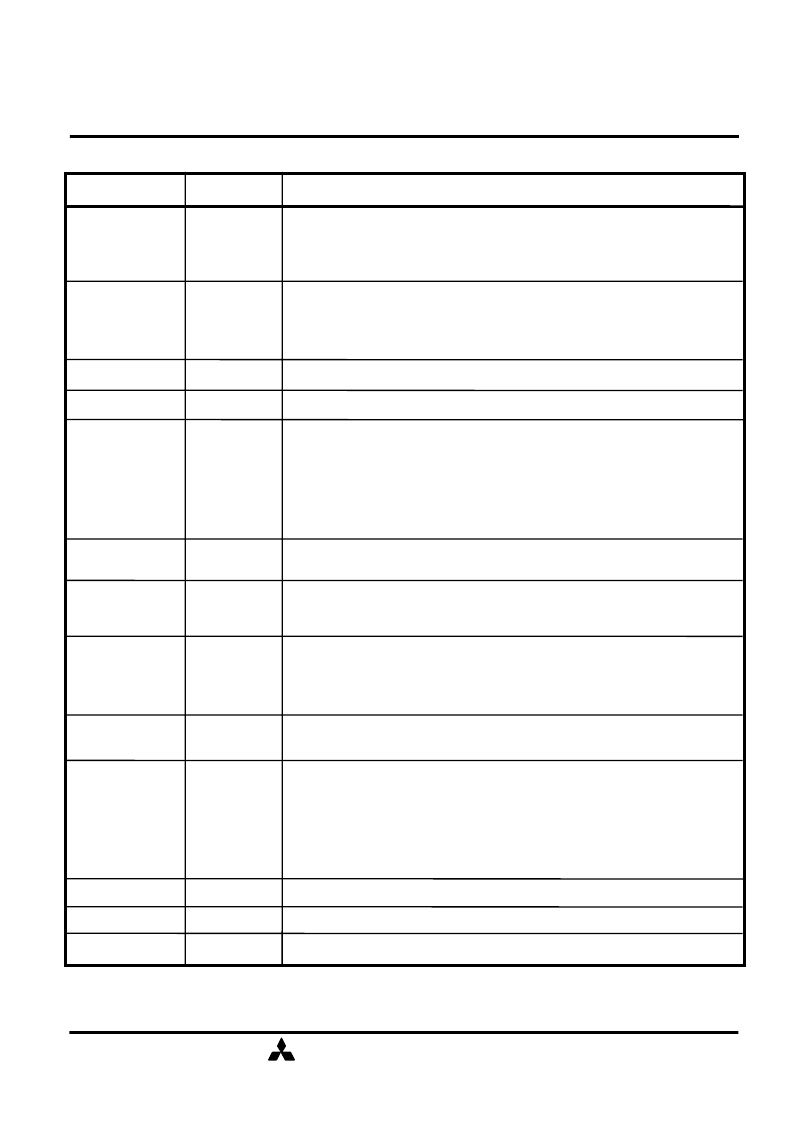

PIN FUNCTION

CLK, /CLK

Input

Clock: CLK and /CLK are differential clock inputs. All address and

control input signals are sampled on the crossing of the positive edge

of CLK and negative edge of /CLK. Output (read) data is referenced to

the crossings of CLK and /CLK (both directions of crossing).

CKE

Input

Clock Enable: CKE controls internal clock. When CKE is low, internal

clock for the following cycle is ceased. CKE is also used to select auto /

self refresh. After self refresh mode is started, CKE becomes

asynchronous input. Self refresh is maintained as long as CKE is low.

/CS

Input

Chip Select: When /CS is high, any command means No Operation.

/RAS, /CAS, /WE

Input

Combination of /RAS, /CAS, /WE defines basic commands.

A0-11

Input

A0-11 specify the Row / Column Address in conjunction with BA0,1.

The Row Address is specified by A0-11. The Column Address is

specified by A0-9,11(x4), A0-9(x8) and A0-8(x16). A10 is also used to

indicate precharge option. When A10 is high at a read / write

command, an auto precharge is performed. When A10 is high at a

precharge command, all banks are precharged.

BA0,1

Input

DQ0-15(x16),

DQ0-7(x8),

DQ0-3(x4),

Input / Output

DQS

Vdd, Vss

Power Supply

Power Supply for the memory array and peripheral circuitry.

VddQ, VssQ

Power Supply

VddQ and VssQ are supplied to the Output Buffers only.

Bank Address: BA0,1 specifies one of four banks to which a command is

applied. BA0,1 must be set with ACT, PRE, READ, WRITE commands.

Data Input/Output: Data bus

Data Strobe: Output with read data, input with write data. Edge-

aligned with read data, centered in write data. Used to capture write

data. For the x16, LDQS corresponds to the data on DQ0-DQ7; UDQS

correspond to the data on DQ8-DQ15

SYMBOL

TYPE

DESCRIPTION

/QFC

Output

FET Control: Optional. Output during every Read and Write access. Can

be used to control isolation switches on modules. Open drain output.

DM

Input

Input Data Mask: DM is an input mask signal for write data. Input data

is masked when DM is sampled HIGH along with that input data

during a WRITE access. DM is sampled on both edges of DQS.

Although DM pins are input only, the DM loading matches the DQ

and DQS loading. For the x16, LDM corresponds to the data on DQ0-

DQ7; UDM corresponds to the data on DQ8-DQ15.

Input / Output

Vref

Input

SSTL_2 reference voltage.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M2V28D30ATP-10 | 353620600 |

| M2V28D30ATP-75 | 128M Double Data Rate Synchronous DRAM |

| M2V28D40ATP-10 | 128M Double Data Rate Synchronous DRAM |

| M2V28D40ATP-75 | 128M Double Data Rate Synchronous DRAM |

| M2S28D20ATP | 128M Double Data Rate Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M2V28D30ATP-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:128M Double Data Rate Synchronous DRAM |

| M2V28D30ATP-75 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:128M Double Data Rate Synchronous DRAM |

| M2V28D40ATP-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:128M Double Data Rate Synchronous DRAM |

| M2V28D40ATP-75 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:128M Double Data Rate Synchronous DRAM |

| M2V28S20ATP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:128M Synchronous DRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。