- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369886 > LXT974QC LAN Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | LXT974QC |

| 英文描述: | LAN Transceiver |

| 中文描述: | 網(wǎng)絡(luò)收發(fā)器 |

| 文件頁數(shù): | 43/68頁 |

| 文件大小: | 1177K |

| 代理商: | LXT974QC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當(dāng)前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

Low-Power Octal PHY

—

LXT9784

Datasheet

43

During reset, all LED drivers are active for approximately 2 seconds, then turned off.

2.11

MII Management Interface Operation

The LXT9784 provides PHY status and accepts PHY management information via the MII

management interface. This is accomplished via read and write operations to various registers

according to the IEEE802.3u Standard. A read or write of a particular register is called a

management frame, which is sent serially over the MDIO pin synchronous to MDC at a maximum

rate of 3 MHz. Read and write cycles are from the perspective of the controller. Therefore, the

controller would always drive the Start, Opcode, PHY Address and Register Address on to the

MDIO pin. For a write, the controller would also drive the transition bits and data. For a read, the

LXT9784 drives the transition bits and data onto the MDIO pin. The controller should drive

address and data on the falling edge of MDC and the LXT9784 latches that data on the rising edge

of MDC. The PHY addresses in the LXT9784 can be configured from 0-31. The management

frame structure is shown in

Table 19

.

This structure allows a controller or other management hardware, to query a PHY for status of the

link, auto-negotiation registers, or configure the PHY to one of many modes.

Table 20

defines the

protocol terms.

When MDIO and MDC are not in use, they should be connected to pull-up devices.

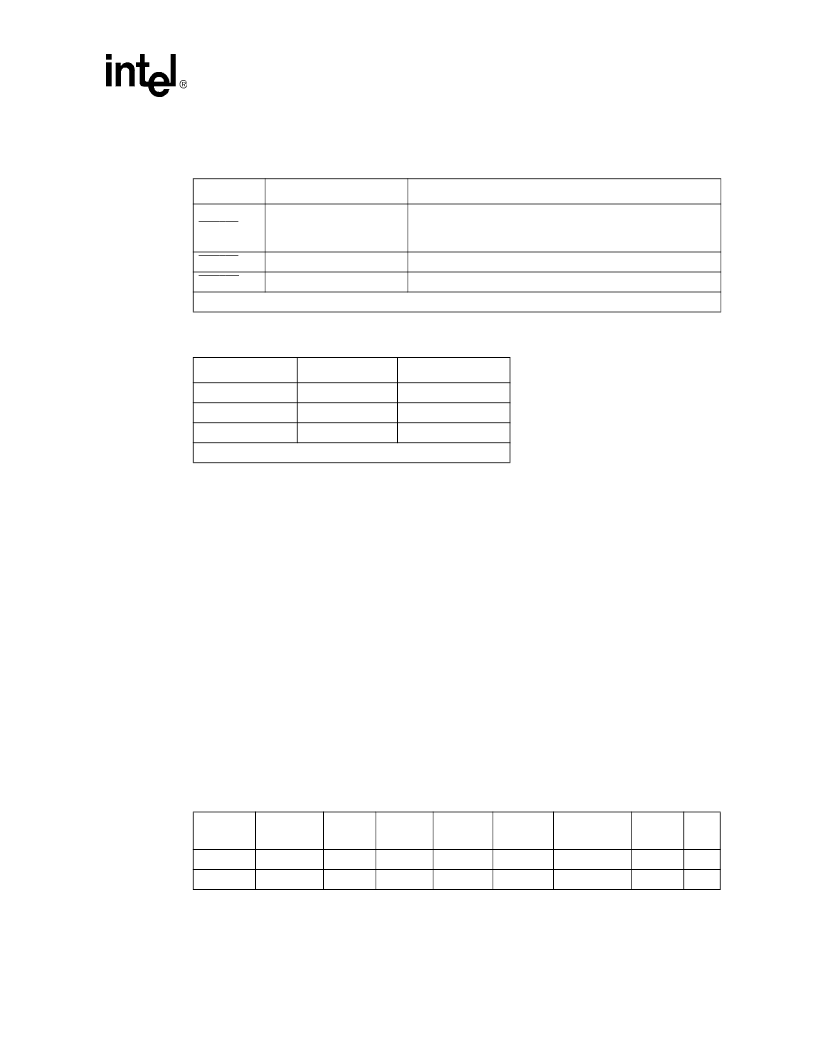

Table 17. LED Functionality

LED driver

Function

Description

LED

n

_A

link

solid

/activity

blink

With a good link the output is low, the output toggles at a rate

related to the utilization.

Refer to

Table 18

for the actual numbers.

LED

n

_B

speed

The output is low for 100 Mbps, high for 10 Mbps

LED

n

_C

collision

The output blinks low with collisions stretch rate of 10 ms.

1.

n

indicates Port Number.

Table 18. Activity LED Blink Rates

Percent Utilization

Blink Rate

1

Frequency

0-5%

slow

3 Hz

5-30%

medium

5 Hz

+30%

fast

7 Hz

1. Note: Duty Cycle = 50%

Table 19. MII Management Frame Format

Function

Preamble

Start

Frame

Opcode

PHY Adr

Reg adr

Turnaround

Data

Idle

READ

1...1

10

10

AAAAA

RRRRR

Z0

D[15:0]

Z

WRITE

1...1

01

01

AAAAA

RRRRR

10

D[15:0]

Z

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT975QC | LAN Transceiver |

| LXT9761 | Interface IC |

| LXT9761HC | LAN TRANSCEIVER|HEX|QFP|208PIN|PLASTIC |

| LXT9762 | Interface IC |

| LXT9762HC | LAN TRANSCEIVER|HEX|QFP|208PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT975 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Fast Ethernet 10/100 Quad Transceivers |

| LXT975A | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Fast Ethernet 10/100 Quad Transceivers |

| LXT975AHC | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Fast Ethernet 10/100 Quad Transceivers |

| LXT975B | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Fast Ethernet 10/100 Quad Transceivers |

| LXT975BHC | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Fast Ethernet 10/100 Quad Transceivers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。