- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369872 > LU3X54FTL-HS208-DB QUAD-FET for 10Base-T/100Base-TX/FX PDF資料下載

參數(shù)資料

| 型號: | LU3X54FTL-HS208-DB |

| 英文描述: | QUAD-FET for 10Base-T/100Base-TX/FX |

| 中文描述: | 四核10Base-T/100Base-TX/FX場效應(yīng)管 |

| 文件頁數(shù): | 32/54頁 |

| 文件大小: | 677K |

| 代理商: | LU3X54FTL-HS208-DB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

LU3X54FT

QUAD-FET for 10Base-T/100Base-TX/FX

Data Sheet

July 2000

32

Lucent Technologies Inc.

MII Station Management

(continued)

Management Registers (MR)

(continued)

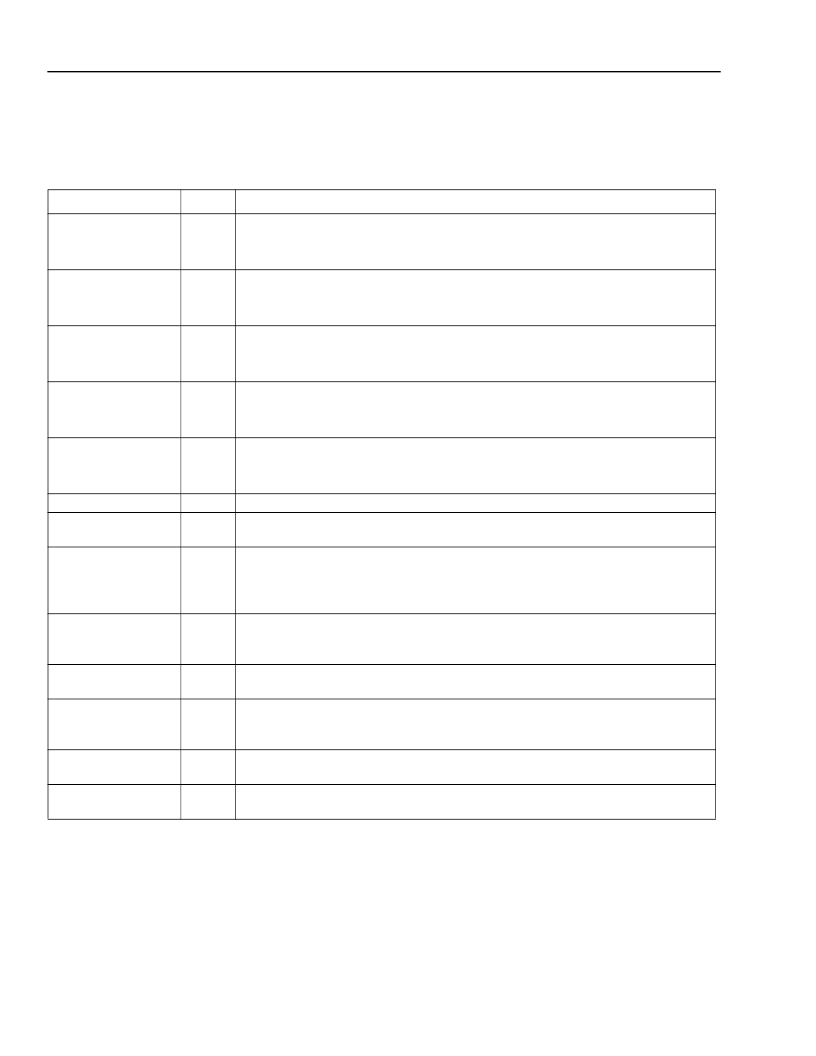

Table 12. MR1—Status Register Bit Descriptions

1. Note that the format for the bit descriptions is as follows: the first number is the register number, the second number is the bit position in the

register, and the name of the instantiated pad is in capital letters.

2. R = read.

Register/Bit

1

1.15 (T4ABLE)

Type

2

R

Description

100Base-T4 Ability.

This bit will always be a 0.

0: Not able.

1: Able.

100Base-TX Full-Duplex Ability.

This bit will always be a 1.

0: Not able.

1: Able.

100Base-TX Half-Duplex Ability.

This bit will always be a 1.

0: Not able.

1: Able.

10Base-T Full-Duplex Ability.

This bit will always be a 1.

0: Not able.

1: Able.

10Base-T Half-Duplex Ability.

This bit will always be a 1.

0: Not able.

1: Able.

Reserved.

All bits will read as a 0.

Suppress Preamble.

This bit is set to a 1 indicating that the LU3X54FT accepts

management frames with the preamble suppressed.

Autonegotiation Complete.

When this bit is a 1, it indicates the autonegotia-

tion process has been completed. The contents of registers MR4, MR5, MR6,

and MR7 are now valid. The default value is a 0. This bit is reset when autone-

gotiation is started.

Remote Fault.

When this bit is a 1, it indicates a remote fault has been

detected. This bit will remain set until cleared by reading the register. The default

is a 0.

Autonegotiation Ability.

When this bit is a 1, it indicates the ability to perform

autonegotiation. The value of this bit is always a 1.

Link Status.

When this bit is a 1, it indicates a valid link has been established.

This bit has a latching function: a link failure will cause the bit to clear and stay

cleared until it has been read via the management interface.

Jabber Detect.

This bit will be a 1 whenever a jabber condition is detected. It

will remain set until it is read, and the jabber condition no longer exists.

Extended Capability.

This bit indicates that the LU3X54FT supports the

extended register set (MR2 and beyond). It will always read a 1.

1.14 (TXFULDUP)

R

1.13 (TXHAFDUP)

R

1.12 (ENFULDUP)

R

1.11 (ENHAFDUP)

R

1.10:7 (RESERVED)

1.6 (NO_PA_OK)

R

R

1.5 (NWAYDONE)

R

1.4 (REM_FLT)

R

1.3 (NWAYABLE)

R

1.2 (LSTAT_OK)

R

1.1 (JABBER)

R

1.0 (EXT_ABLE)

R

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LU3X54FT | Quad-FET (Fast Ethernet Transceiver) for 10Base-T/100Base-TX/FX(應(yīng)用于10基數(shù)-T和100基數(shù)-TX/FX的四快速以太網(wǎng)收發(fā)器) |

| LU5X34F | Quad Gigabit Ethernet Transceiver |

| LU5X34F | Quad Gigabit Ethernet Transceiver(千兆位以太網(wǎng)四收發(fā)器) |

| LUCL8551AAU | Subscriber Line Interface Circuit |

| LUCL8551AP | Subscriber Line Interface Circuit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LU3X54FTLHS208-DB | 制造商:Alcatel-Lucent 功能描述:3X54FTLHS208-DB |

| LU400 | 制造商:MA-COM 制造商全稱:M/A-COM Technology Solutions, Inc. 功能描述:NEMA Cabinet Legs |

| LU400/D | 制造商:OSRAM 功能描述:400W MOGUL BASED GENERAL LIGHTING HIGH PRESSURE SODIUM LAMP, COATED, DAYLIGHT, U |

| LU400/PLUS/ECO | 制造商:OSRAM 功能描述:400W NON CYCLING, ENVIRONMENTALLY FRIENDLIER HIGH PRESSURE SODIUM LAMP, CLEAR, U |

| LU47 | 制造商:Thomas & Betts 功能描述:1-1/4 CONDUIT BODY,IRON,LU,F-7 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。