- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369872 > LU3X54FTL-HS208-DB QUAD-FET for 10Base-T/100Base-TX/FX PDF資料下載

參數(shù)資料

| 型號(hào): | LU3X54FTL-HS208-DB |

| 英文描述: | QUAD-FET for 10Base-T/100Base-TX/FX |

| 中文描述: | 四核10Base-T/100Base-TX/FX場(chǎng)效應(yīng)管 |

| 文件頁(yè)數(shù): | 27/54頁(yè) |

| 文件大小: | 677K |

| 代理商: | LU3X54FTL-HS208-DB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)

Lucent Technologies Inc.

27

Data Sheet

July 2000

LU3X54FT

QUAD-FET for 10Base-T/100Base-TX/FX

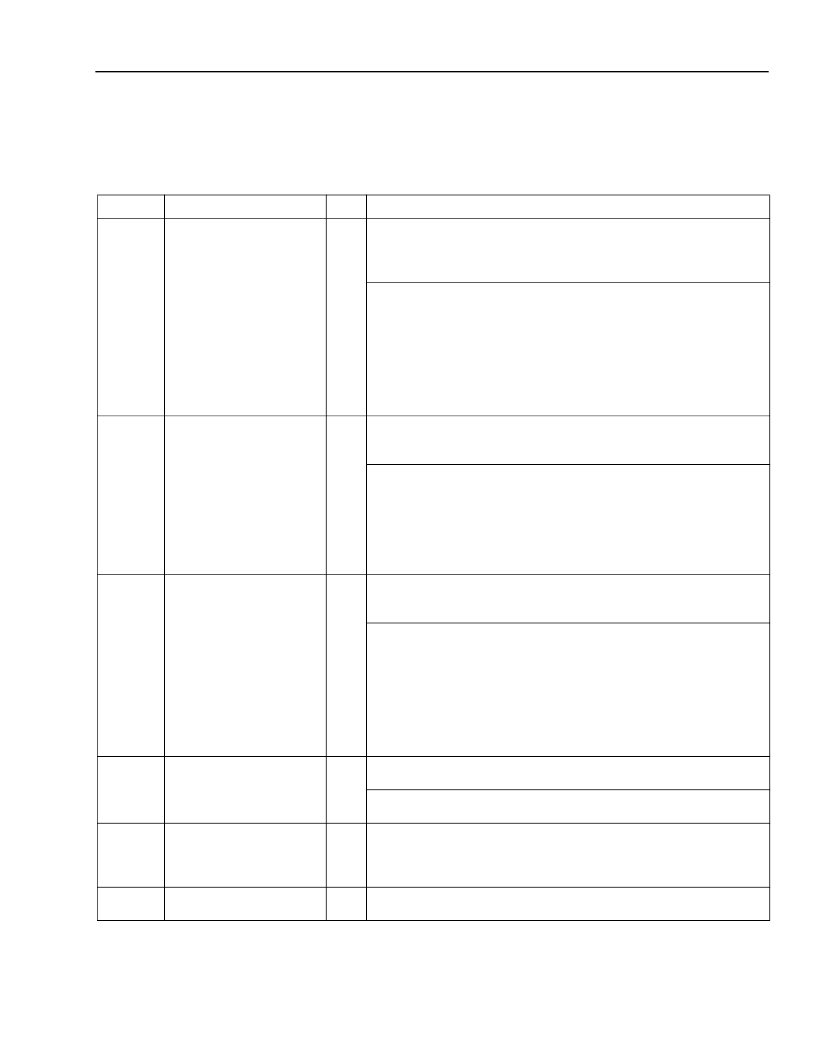

191

SPEEDLED[A]/

ISOLATE_MODE

I/O

Speed LED[A].

This pin indicates the operating speed of port A on the

LU3X54FT. A high on this pin indicates 100 Mbits/s operation. A low

indicates 10 Mbits/s operation. External buffers are necessary to drive

the LEDs.

Isolate Mode.

As an input, this pin can be used at powerup or reset to

select the isolate operation mode. If this pin is pulled high through a

4.7 k

resistor, the LU3X54FT will powerup or reset to the isolate

mode. (MII outputs to high-impedance state.)

This pin is internally pulled low through a 50 k

resistor. The default

state is for the LU3X54FT to powerup or reset in a nonisolate mode.

This pin and register bit [10.0] are ORed together during powerup and

reset.

Half-Duplex LED[D].

When this output is high, it indicates half-duplex

mode. When it is low, it indicates full duplex. External buffers are nec-

essary to drive the LEDs. This output is only valid when the link is up.

Full Duplex.

At powerup, this pin may be used to select full-duplex

operation for all four channels by pulling it high through a 4.7 k

resis-

tor, if station management is unavailable. This is the same function as

register 0, bit 8. This pin has an internal 50 k

pull-down resistor to

default to half duplex for normal operation. This input and the register

bit [0.8] are ORed together during powerup and reset. This pin is

ignored when autonegotiation is enabled.

Half-Duplex LED[A].

When this output is high, it indicates half-duplex

mode. When low, it indicates full duplex. External buffers are necessary

to drive the LEDs. This output is only valid when the link is up.

20 MHz Clock Select.

When this signal is pulled high through a

4.7 k

resistor, it will enable the two-clock input mode (20 MHz and

25 MHz). This pin is internally pulled low through a 50 k

resistor to set

the default to internal 20 MHz. When low, this signal enables the single-

clock input mode (25 MHz with 20 MHz clock internally generated).

201

H_DUPLED[D]/

FULL_DUP

I/O

198

H_DUPLED[A]/

CLK20_SEL

I/O

This pin has the same function as register 30, bit 6, if station manage-

ment is unavailable. This input and the register bit [30.6] are ORed

together during powerup and reset.

CMOS Local Symbol Clock.

A 25 MHz clock,

±

100 ppm, 40%—60%

duty cycle.

Crystal Oscillator Input.

A 25 MHz crystal ±25 ppm can be connected

across XTALIN and XTALOUT.

Crystal Oscillator Output.

A 25 MHz crystal ±25 ppm can be con-

nected across XTALIN and XTALOUT. If a single-ended external clock

(LSCLK) is connected to XTALIN, the crystal output pin should be left

floating.

Test Mode Select.

Reserved for manufacturing testing. These pins

should be tied low for normal operation.

87

LSCLK/XTALIN

I

88

XTALOUT

I

55

207—204

MODE[4:0]

I

Pin Information

(continued)

Pin Descriptions

(continued)

Table 7. Miscellaneous Pins

(continued)

Pin

Signal

Type

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LU3X54FT | Quad-FET (Fast Ethernet Transceiver) for 10Base-T/100Base-TX/FX(應(yīng)用于10基數(shù)-T和100基數(shù)-TX/FX的四快速以太網(wǎng)收發(fā)器) |

| LU5X34F | Quad Gigabit Ethernet Transceiver |

| LU5X34F | Quad Gigabit Ethernet Transceiver(千兆位以太網(wǎng)四收發(fā)器) |

| LUCL8551AAU | Subscriber Line Interface Circuit |

| LUCL8551AP | Subscriber Line Interface Circuit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LU3X54FTLHS208-DB | 制造商:Alcatel-Lucent 功能描述:3X54FTLHS208-DB |

| LU400 | 制造商:MA-COM 制造商全稱:M/A-COM Technology Solutions, Inc. 功能描述:NEMA Cabinet Legs |

| LU400/D | 制造商:OSRAM 功能描述:400W MOGUL BASED GENERAL LIGHTING HIGH PRESSURE SODIUM LAMP, COATED, DAYLIGHT, U |

| LU400/PLUS/ECO | 制造商:OSRAM 功能描述:400W NON CYCLING, ENVIRONMENTALLY FRIENDLIER HIGH PRESSURE SODIUM LAMP, CLEAR, U |

| LU47 | 制造商:Thomas & Betts 功能描述:1-1/4 CONDUIT BODY,IRON,LU,F-7 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。