- 您現(xiàn)在的位置:買賣IC網 > PDF目錄369872 > LU3X54FTL-HS208-DB QUAD-FET for 10Base-T/100Base-TX/FX PDF資料下載

參數資料

| 型號: | LU3X54FTL-HS208-DB |

| 英文描述: | QUAD-FET for 10Base-T/100Base-TX/FX |

| 中文描述: | 四核10Base-T/100Base-TX/FX場效應管 |

| 文件頁數: | 26/54頁 |

| 文件大?。?/td> | 677K |

| 代理商: | LU3X54FTL-HS208-DB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

LU3X54FT

QUAD-FET for 10Base-T/100Base-TX/FX

Data Sheet

July 2000

26

Lucent Technologies Inc.

194

SPEEDLED[D]/

SPEED

I/O

Speed LED[D].

This pin indicates the operating speed of port D on the

LU3X54FT. A high on this pin indicates 100 Mbits/s operation. A low

indicates 10 Mbits/s operation. External buffers are necessary to drive

the LEDs.

Speed.

This pin is used at powerup or reset to select the operating

speed on all four channels and is the same function as register 0,

bit 13:

I

This pin is internally pulled high through a 100 k

resistor to enable

100 Mbits/s operation (defaults to 100 Mbits/s).

I

If this pin is pulled low through a 4.7 k

resistor, it will enable

10 Mbits/s operation.

This pin is ignored when autonegotiation is enabled. This pin and the

register bit are ANDed.

Speed LED[C].

This pin indicates the operating speed of port C on the

LU3X54FT. A high on this pin indicates 100 Mbits/s operation. A low

indicates 10 Mbits/s operation. External buffers are necessary to drive

the LEDs.

Smart Mode Select.

At powerup or reset, if this pin is pulled high

through a 4.7 k

resistor, the smart mode will be selected which

enables the use of the security feature and redefines the CRS, COL,

and TX_EN10 pins. This pin is internally pulled low through a 50 k

pull-down resistor. The default value is SMART_MODE _SELECT dis-

abled.

193

SPEEDLED[C]/

SMART_MODE_SELECT

I/O

When SMART_MODE_SELECT is asserted, the TX_EN10 inputs are

used as the security inputs for both 10 Mbits/s mode and 100 Mbits/s

mode. When security is activated high, the LU3X54FT will transmit a

jam signal instead of data.

When SMART_MODE_SELECT is asserted high, both the CRS_10

and CRS_100 signals will be output on the CRS_100 pins, and both

the COL_10 and COL_100 signals will be output on the COL_100 pins.

Speed LED[B].

This pin indicates the operating speed of port B on the

LU3X54FT. A high on this pin indicates 100 Mbits/s operation. A low

indicates 10 Mbits/s operation. External buffers are necessary to drive

the LEDs.

Bused MII Mode Select.

At powerup or reset, if the bused MII mode

select pin is pulled high through a 4.7 k

resistor, data streams from

ports running at 100 Mbits/s will appear on the single 100 Mbits/s MII

(port A), and data streams from ports running at 10 Mbits/s will appear

at the single 10 Mbits/s serial interface (port B). In addition, control sig-

nals TX_EN10, TX_EN100, RX_EN10, RX_EN100, CRS_10, and

CRS_100 become active.

192

SPEEDLED[B]/

BUSED_MII_MODE

I/O

This pin is internally pulled low through a 50 k

pull-down resistor. The

default value is bused mode disabled.

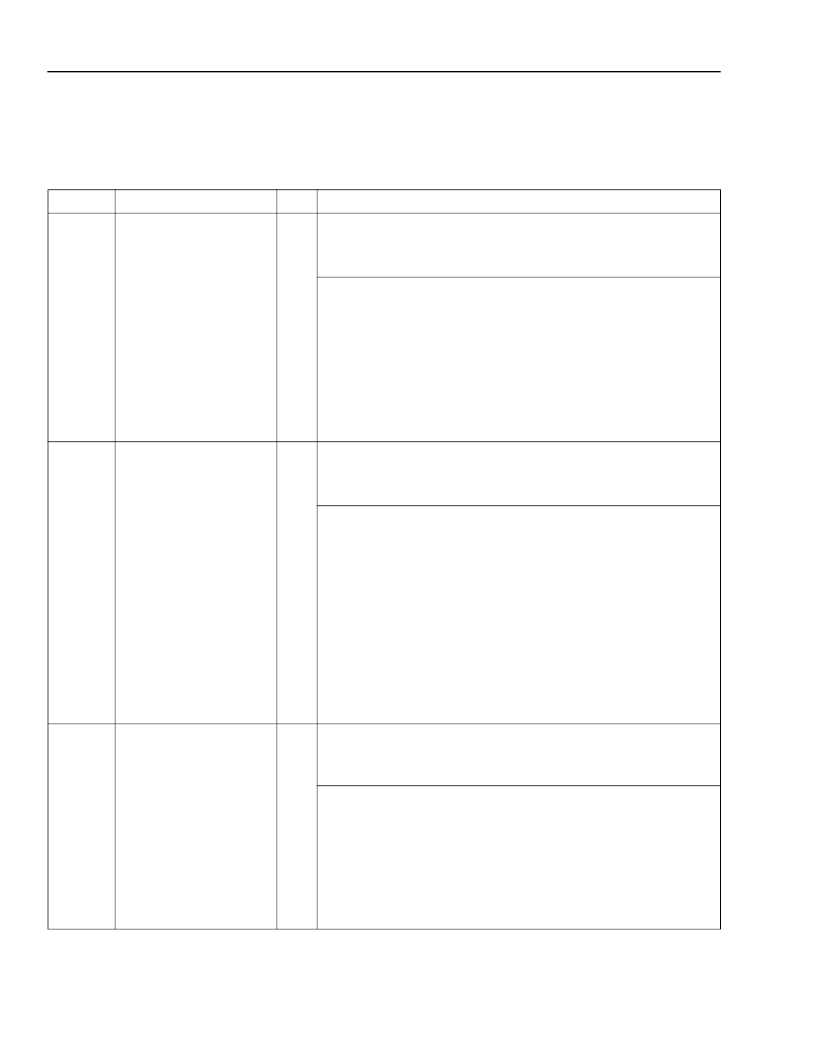

Pin Information

(continued)

Pin Descriptions

(continued)

Table 7. Miscellaneous Pins

(continued)

Pin

Signal

Type

Description

相關PDF資料 |

PDF描述 |

|---|---|

| LU3X54FT | Quad-FET (Fast Ethernet Transceiver) for 10Base-T/100Base-TX/FX(應用于10基數-T和100基數-TX/FX的四快速以太網收發(fā)器) |

| LU5X34F | Quad Gigabit Ethernet Transceiver |

| LU5X34F | Quad Gigabit Ethernet Transceiver(千兆位以太網四收發(fā)器) |

| LUCL8551AAU | Subscriber Line Interface Circuit |

| LUCL8551AP | Subscriber Line Interface Circuit |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LU3X54FTLHS208-DB | 制造商:Alcatel-Lucent 功能描述:3X54FTLHS208-DB |

| LU400 | 制造商:MA-COM 制造商全稱:M/A-COM Technology Solutions, Inc. 功能描述:NEMA Cabinet Legs |

| LU400/D | 制造商:OSRAM 功能描述:400W MOGUL BASED GENERAL LIGHTING HIGH PRESSURE SODIUM LAMP, COATED, DAYLIGHT, U |

| LU400/PLUS/ECO | 制造商:OSRAM 功能描述:400W NON CYCLING, ENVIRONMENTALLY FRIENDLIER HIGH PRESSURE SODIUM LAMP, CLEAR, U |

| LU47 | 制造商:Thomas & Betts 功能描述:1-1/4 CONDUIT BODY,IRON,LU,F-7 |

發(fā)布緊急采購,3分鐘左右您將得到回復。