- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373155 > KM418RD32D (SAMSUNG SEMICONDUCTOR CO. LTD.) 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM PDF資料下載

參數(shù)資料

| 型號: | KM418RD32D |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| 中文描述: | 128/144Mbit RDRAM的256 × 16/18位× 2 * 16屬銀行直接RDRAMTM |

| 文件頁數(shù): | 16/64頁 |

| 文件大小: | 4052K |

| 代理商: | KM418RD32D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

Page 13

KM416RD8AC(D)/KM418RD8AC(D)

Direct RDRAM

Rev. 1.01 Oct. 1999

ROW-to-ROW Interaction - contin-

ued

Cases RR13 through RR16 summarize the combinations of

two successive PRER commands. In case RR13 there is no

restriction since two devices are addressed. In RR14, t

PP

applies, since the same device is addressed. In RR15 and

RR16, the same bank or an adjacent bank may be given

repeated PRER commands with only the t

PP

restriction.

Two adjacent banks can’t be activate simultaneously. A

precharge command to one bank will thus affect the state of

the adjacent banks (and sense amps). If bank Ba is activate

and a PRER is directed to Ba, then bank Ba will be

precharged along with sense amps Ba-1/Ba and Ba/Ba+1. If

bank Ba+1 is activate and a PRER is directed to Ba, then

bank Ba+1 will be precharged along with sense amps

Ba/Ba+1 and Ba+1/Ba+2. If bank Ba-1 is activate and a

PRER is directed to Ba, then bank Ba-1 will be precharged

along with sense amps Ba/Ba-1 and Ba-1/Ba-2.

A ROW packet may contain commands other than ACT or

PRER. The REFA and REFP commands are equivalent to

ACT and PRER for interaction analysis purposes. The inter-

action rules of the NAPR, NAPRC, PDNR, RLXR, ATTN,

TCAL, and TCEN commands are discussed in later sections

(see Table 7 for cross-ref).

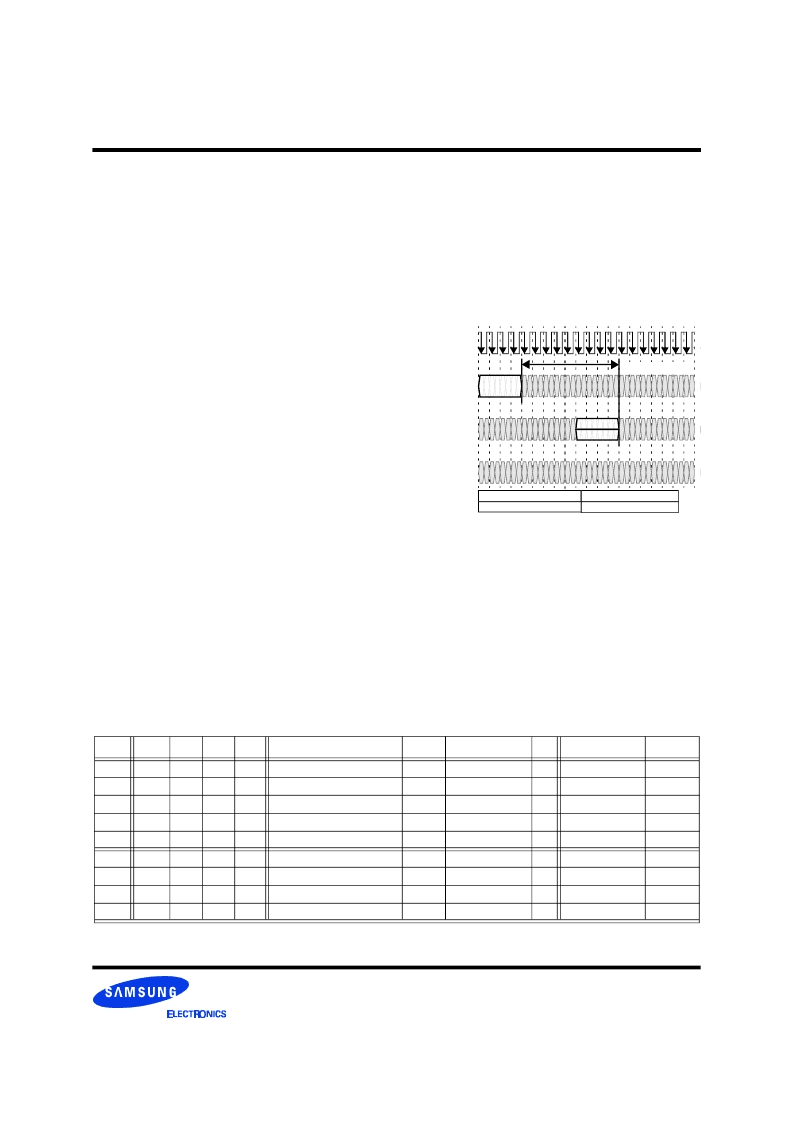

ROW-to-COL Packet Interaction

Figure 7 shows two packets on the ROW and COL pins.

They must be separated by an interval t

RCDELAY

which

depends upon the packet contents. Table 11 summarizes the

t

RCDELAY

values for all possible cases. Note that if the COL

packet is earlier than the ROW packet, it is considered a

COL-to-ROW packet interaction.

Cases RC1 through RC5 summarize the rules when the

ROW packet has an ACT command. Figure 15 and

Figure 16 show examples of RC5 - an activation followed by

a read or write. RC4 is an illegal situation, since a read or

write of a precharged banks is being attempted (remember

that for a bank to be activated, adjacent banks must be

precharged). In cases RC1, RC2, and RC3, there is no inter-

action of the ROW and COL packets.

Cases RC6 through RC8 summarize the rules when the

ROW packet has a PRER command. There is either no inter-

action (RC6 through RC9) or an illegal situation with a read

or write of a precharged bank (RC9).

The COL pins can also schedule a precharge operation with

a RDA, WRA, or PREC command in a COLC packet or a

PREX command in a COLX packet. The constraints of these

precharge operations may be converted to equivalent PRER

command constraints using the rules summarized in

Figure 14.

Figure 7: ROW-to-COL Packet Interaction- Timing

CTM/CFM

DQA8..0

DQB8..0

COL4

..COL0

ROW2

..ROW0

T

0

T

4

T

8

T

12

T

1

T

5

T

9

T

13

T

2

T

6

T

10

T

14

T

3

T

7

T

11

T

15

T

16

T

T

17

T

18

T

19

Transaction a: ROPa

Transaction b: COPb

a0 = {Da,Ba,Ra}

b1= {Db,Bb,Cb1}

t

RCDELAY

ROPa a0

COPb b1

Table 11: ROW-to-COL Packet Interaction - Rules

Case #

ROPa

Da

Ba

Ra

COPb

Db

Bb

Cb1

t

RCDELAY

Example

RC1

ACT

Da

Ba

Ra

NOCOP,RD,retire

/= Da

xxxx

x..x

0

RC2

ACT

Da

Ba

Ra

NOCOP

== Da

xxxx

x..x

0

RC3

ACT

Da

Ba

Ra

RD,retire

== Da

/= {Ba,Ba+1,Ba-1}

x..x

0

RC4

ACT

Da

Ba

Ra

RD,retire

== Da

== {Ba+1,Ba-1}

x..x

Illegal

RC5

ACT

Da

Ba

Ra

RD,retire

== Da

== Ba

x..x

t

RCD

Figure 15

RC6

PRER

Da

Ba

Ra

NOCOP,RD,retire

/= Da

xxxx

x..x

0

RC7

PRER

Da

Ba

Ra

NOCOP

== Da

xxxx

x..x

0

RC8

PRER

Da

Ba

Ra

RD,retire

== Da

/= {Ba,Ba+1,Ba-1}

x..x

0

RC9

PRER

Da

Ba

Ra

RD,retire

== Da

== {Ba+1,Ba-1}

x..x

Illegal

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KM418RD4AC | 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM418RD4AD | 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM418RD4C | 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM418RD4D | 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM416RD16AD | CAP ELECT 47UF 100V TG SMD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KM418RD4AC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM418RD4AD | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM418RD4C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM418RD4D | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM418RD8AC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。